## Primterme und Kernimplikanten

Gegeben ist die durch das folgende KV-Diagramm partiell definierte Funktion F.

|   |                  |          |          |                 |                 | <u> </u>        |                 |                 |   |

|---|------------------|----------|----------|-----------------|-----------------|-----------------|-----------------|-----------------|---|

|   | $\boldsymbol{F}$ | A        | <u>A</u> |                 |                 |                 |                 |                 |   |

|   | 10               | 1 1      | $1_5$    | $X_4$           | 1 <sub>20</sub> | $X_{21}$        | 1 <sub>17</sub> | $0_{16}$        |   |

|   | $0_2$            | $X_3$    | 1,       | $0_6$           | $0_{\!22}$      | 1 <sub>23</sub> | 1 <sub>19</sub> | $0_{\!18}$      | D |

| D | $O_{10}$         | $1_{11}$ | $0_{15}$ | 1 <sub>14</sub> | $X_{30}$        | $0_{31}$        | $X_{27}$        | $0_{26}$        | B |

|   | $X_8$            | $0_9$    | $0_{13}$ | $0_{12}$        | $0_{\!28}$      | $0_{29}$        | $0_{25}$        | 1 <sub>24</sub> |   |

|   |                  | -        |          | (               | 7               |                 |                 |                 |   |

- a) Bestimmen Sie die Primterme der Funktion F. Tragen Sie dazu die Einser-Blöcke in das KV-Diagramm ein und notieren Sie die entsprechenden Terme!

- b) Bestimmen Sie die Kernimplikanten der Funktion F. Geben Sie für jeden Kernimplikanten an, aufgrund welcher Minterme Sie diesen Kernimplikanten als solchen identifiziert haben !

#### Entwurf eines Schaltnetzes

Für eine spezielle Anwendung wird eine Schaltung benötigt, welche die mathematische Operation

$$C = A + B + A \cdot B$$

ausführt. Dabei stellen A und B jeweils eine Dualzahl mit einer Wortbreite von 2 Bit  $(A = \{A_1, A_0\}; B = \{B_1, B_0\})$  dar. Bei dem Ergebnis C handelt es sich ebenfalls um eine Dualzahl, jedoch mit einer Wortbreite von 4 Bit  $(C = \{C_3, C_2, C_1, C_0\})$ .

Aus bestimmten Gründen können die Wertekombinationen

$$A=0 \quad \text{und} \quad B=2 \qquad \text{(d.h. } A_1=A_0=B_0=0 \ \text{und} \ B_1=1) \quad \text{und} \ A=2 \quad \text{und} \quad B=0 \qquad \text{(d.h. } A_1=1 \ \text{und} \ A_0=B_1=B_0=0)$$

nicht auftreten. Daher können die Schaltungsausgänge  $C_3$ ,  $C_2$ ,  $C_1$  und  $C_0$  in diesen beiden Fällen einen beliebigen Wert annehmen.

a) Tragen Sie die Zustände der Ausgänge  $C_3$ ,  $C_2$ ,  $C_1$  und  $C_0$  in die nachfolgende Tabelle ein. Kennzeichnen Sie dabei den Zustand 'beliebig' durch das Symbol 'X'.

|    | Signal-  |       | Steuer- |       | Signal-  |       |       |       |

|----|----------|-------|---------|-------|----------|-------|-------|-------|

|    | eingänge |       | eing    | änge  | ausgänge |       |       |       |

| #  | $A_1$    | $A_0$ | $B_1$   | $B_0$ | $C_3$    | $C_2$ | $C_1$ | $C_0$ |

| 0  | 0        | 0     | 0       | 0     |          |       |       |       |

| 1  | 0        | 0     | 0       | 1     |          |       |       |       |

| 2  | 0        | 0     | 1       | 0     |          |       |       |       |

| 3  | 0        | 0     | 1       | 1     |          |       |       |       |

| 4  | 0        | 1     | 0       | 0     |          |       |       |       |

| 5  | 0        | 1     | 0       | 1     |          |       |       |       |

| 6  | 0        | 1     | 1       | 0     |          |       |       |       |

| 7  | 0        | 1     | 1       | 1     |          |       |       |       |

| 8  | 1        | 0     | 0       | 0     |          |       |       |       |

| 9  | 1        | 0     | 0       | 1     |          |       |       |       |

| 10 | 1        | 0     | 1       | 0     |          |       |       |       |

| 11 | 1        | 0     | 1       | 1     |          |       |       |       |

| 12 | 1        | 1     | 0       | 0     |          |       |       |       |

| 13 | 1        | 1     | 0       | 1     |          |       |       |       |

| 14 | 1        | 1     | 1       | 0     |          |       |       |       |

| 15 | 1        | 1     | 1       | 1     |          |       |       |       |

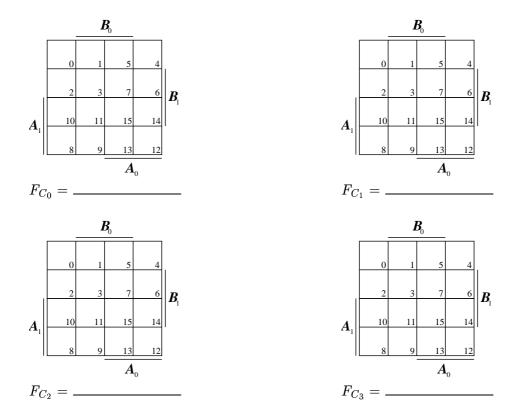

b) Übertragen Sie nun die Zustände in die nachfolgend abgebildeten KV-Diagramme und verwenden sie diese anschließend zur Minimierung der Ausgangsfunktionen. Nutzen Sie dabei die Ausgangszustände beliebig ('X') möglichst geschickt aus, um die Funktionen zu minimieren. Tragen Sie anschließend die 4 optimierten Ausgangsgleichungen  $F_{C_0}$ ,  $F_{C_1}$ ,  $F_{C_2}$  und  $F_{C_3}$  in die vorgesehenen Felder ein.

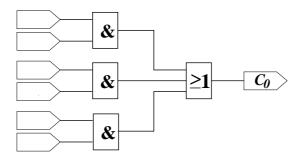

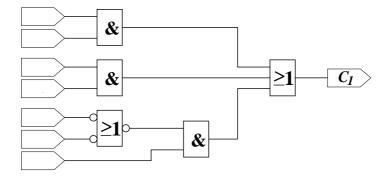

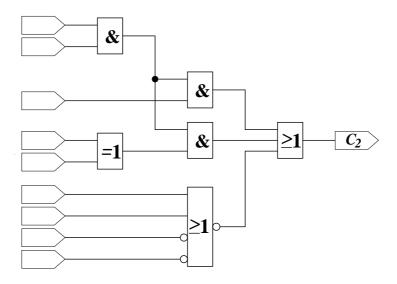

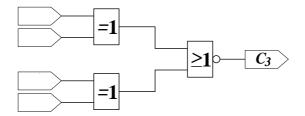

c) Zur Realisierung der Ansteuerschaltungen für die 4 Ausgänge  $C_3$ ,  $C_2$ ,  $C_1$  und  $C_0$  stehen Ihnen nun vier Schaltungsblöcke zur Verfügung. Beschalten Sie die Eingänge der Schaltungsblöcke so, dass diese das Schaltverhalten gemäß den Ausgangsgleichungen  $F_{C_3}$ ,  $F_{C_2}$ ,  $F_{C_1}$  und  $F_{C_0}$  besitzen.

Tragen Sie hierzu in den nachfolgenden Abbildungen die Bezeichungen der Eingangsignale in die dafür vorgesehenen Pfeile ein. Als Bezeichnungen dürfen Sie  $A_1$ ,  $A_0$ ,  $B_1$  und  $B_0$ , sowie die konstanten Signale 1 und 0 verwenden. Beachten Sie, dass Ihnen die Signale nur in der genannten und nicht in negierter Form zur Verfügung stehen. Schaltungsblock zur Realisierung der Schaltfunktion  $F_{C_0}$ :

Schaltungsblock zur Realisierung der Schaltfunktion  $F_{C_1}$ :

Schaltungsblock zur Realisierung der Schaltfunktion  $F_{C_2}$ :

Schaltungsblock zur Realisierung der Schaltfunktion  $F_{C_3}$ :

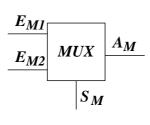

d) Die Ausgangssignale können anstatt mit UND/ODER-Gattern auch mit Hilfe von 2-auf-1-Multiplexern erzeugt werden. Zeigen Sie dies exemplarisch für die Ausgangssignale  $C_0$  und  $C_3$ , indem Sie jeweils eine entsprechende Schaltung, die nur aus 2-auf-1-Multiplexern besteht, entwerfen. Beachten Sie, dass Sie an die Eingänge der Multiplexer auch das konstante Eingangssignal '0' oder '1' anlegen dürfen! Die zur Verfügung stehenden Multiplexerbausteine besitzen einen Signalausgang  $A_M$ , einen Steuereingang  $S_M$  und die beiden Signaleingänge  $E_{M1}$  und  $E_{M2}$ . Für das Ausgangssignal gilt:

$$A_M = \left\{ egin{array}{ll} E_{M1} & : & S_M = 0 \\ E_{M2} & : & S_M = 1 \end{array}

ight.$$

Skizzieren Sie die beiden Schaltungen!

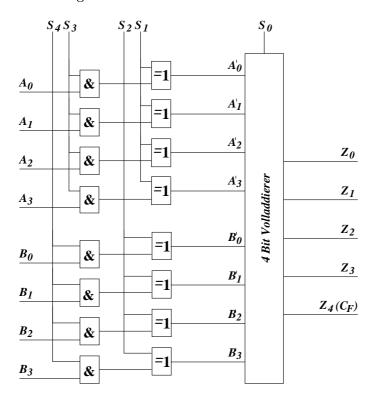

### Addierschaltung

Gegeben ist das nachfolgend abgebildete Addierwerk. Mit Hilfe der Steuereingänge  $S_4$ ,  $S_3$ ,  $S_2$ ,  $S_1$  und  $S_0$  kann eine Operation ausgewählt werden, die auf die beiden dual kodierten Eingabewerte A und B angewendet wird.

a) In der nachfolgend abgebildeten Tabelle sind zulässige Wertekombinationen für die Steuereingänge aufgeführt. Identifizieren Sie die zugehörige Operation, indem Sie den Ausgabewert Z als Funktion der Eingabewerte A und B beschreiben. Beachten Sie, dass der Ausgabewert Z nicht in jedem Fall von A bzw. B abhängt. Sowohl bei A und B, als auch bei Z handelt es sich um dual kodierte Zahlenwerte in Zweierkomplement-Darstellung.

| $S_4$ | $S_3$ | $S_2$ | $S_1$ | $S_0$ | Z = f(A, B) |

|-------|-------|-------|-------|-------|-------------|

| 0     | 0     | 0     | 0     | 1     |             |

| 0     | 1     | 0     | 0     | 0     |             |

| 0     | 1     | 0     | 1     | 1     |             |

| 1     | 0     | 0     | 0     | 1     |             |

| 1     | 0     | 1     | 0     | 1     |             |

| 1     | 1     | 0     | 0     | 0     |             |

| 1     | 1     | 0     | 0     | 1     |             |

| 1     | 1     | 1     | 0     | 1     |             |

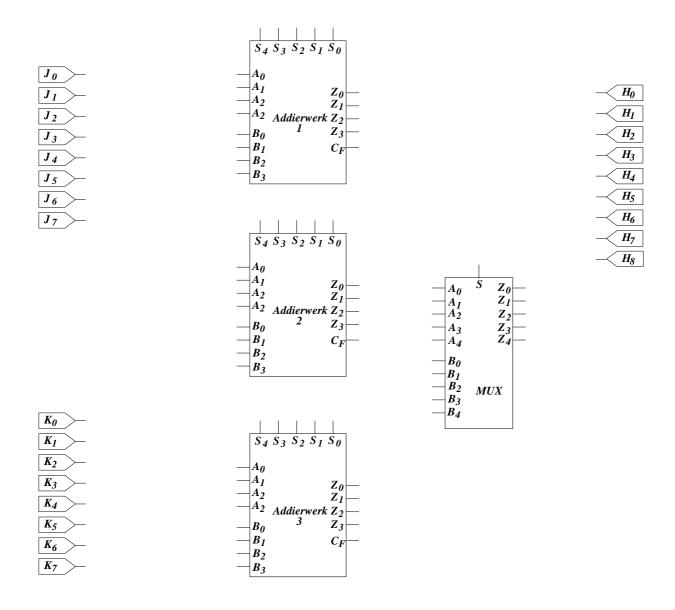

b) Nun soll mit Hilfe dreier 4-Bit-Addierwerke und einem Multiplexer ein 8-Bit-Volladdierer aufgebaut werden. Die dual kodierten Eingabewerte J und K besitzen eine Wortbreite von 8 Bit, das Ergebnis H eine Wortbreite von 9 Bit. Addierwerk 1 soll die niederwertigen Bits der Eingabewerte J und K addieren. Die Addierwerke 2 und 3 sollen zur Addition der 4 höherwertigen Bits verwendet werden, wobei einmal der Übertragseingang  $(S_0)$  gleich '0' und einmal '1' sein soll. Der Multiplexer soll anhand des Übertragsergebnisses der Addition der niederwertigen Bits von den Additionsergebnissen der Schaltwerke 2 und 3 das korrekte Ergebnis der 4 höherwertigen Bits auswählen.

Vervollständigen Sie das Schaltbild der nachfolgenden Abbildung, indem Sie die fehlenden Verbindungen eintragen bzw. die Eingänge auf logisch '0' oder '1' setzen (z.B. durch Angabe von '0' oder '1' an dem jeweiligen Eingang). Unbeschaltete Eingänge werden als fehlerhaft angesehen. Beachten Sie, dass der Multiplexer bei S=1 die Eingangssignale  $B_0,\ldots,B_4$  auf die Ausgänge  $Z_0,\ldots,Z_4$  schaltet.

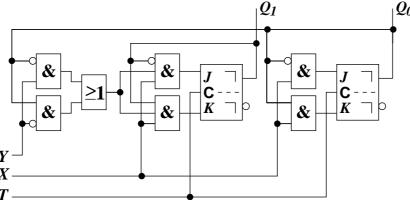

#### Schaltwerksanalyse

Gegeben ist das unten abgebildete synchrone Schaltwerk mit JK-MS-Flipflops, welches in der Folge analysiert werden soll. Ausgangsgröße sei die dual kodierte Zustandsnummer  $(Q_1 Q_0)|_2$ .

- a) Um welchen Automatentyp handelt es sich bei dem gezeigten Schaltwerk? Kreuzen Sie die entsprechende richtige Antwort an und begründen Sie kurz ihre Antwort:

- □ Es handelt sich weder um einen Moore-Automaten, noch um einen Mealy-Automaten.

- □ Das Schaltwerk ist der Definition nach ein Moore-Automat, allerdings kein Mealy-Automat.

- □ Das Schaltwerk ist der Definition nach ein Mealy-Automat, allerdings kein Moore-Automat.

- □ Das Schaltwerk ist der Definition nach sowohl ein Moore-Automat als auch ein Mealy-Automat.

- b) Geben Sie die Funktionsgleichungen für alle Flipflop-Eingänge in Abhängigkeit von  $Q_1$ ,  $Q_0$ , X und Y an. Dabei bezeichnen  $J_0$ ,  $K_0$  die Eingänge von FF0 (FF mit Ausgang  $Q_0$ ),  $J_1$  und  $K_1$  entsprechend die von FF1 (FF mit Ausgang  $Q_1$ ).

- c) Vervollständigen Sie die folgende Zustandstabelle des Schaltwerks.

| X | Y | $Q_1$ | $Q_0$ | $J_1$ | $K_1$ | $J_0$ | $K_0$ | $Q_1^+$ | $Q_0^+$ |

|---|---|-------|-------|-------|-------|-------|-------|---------|---------|

| 0 | 0 | 0     | 0     |       |       |       |       |         |         |

| 0 | 0 | 0     | 1     |       |       |       |       |         |         |

| 0 | 0 | 1     | 0     |       |       |       |       |         |         |

| 0 | 0 | 1     | 1     |       |       |       |       |         |         |

| 0 | 1 | 0     | 0     |       |       |       |       |         |         |

| 0 | 1 | 0     | 1     |       |       |       |       |         |         |

| 0 | 1 | 1     | 0     |       |       |       |       |         |         |

| 0 | 1 | 1     | 1     |       |       |       |       |         |         |

| 1 | 0 | 0     | 0     |       |       |       |       |         |         |

| 1 | 0 | 0     | 1     |       |       |       |       |         |         |

| 1 | 0 | 1     | 0     |       |       |       |       |         |         |

| 1 | 0 | 1     | 1     |       |       |       |       |         |         |

| 1 | 1 | 0     | 0     |       |       |       |       |         |         |

| 1 | 1 | 0     | 1     |       |       |       |       |         |         |

| 1 | 1 | 1     | 0     |       |       |       |       |         |         |

| 1 | 1 | 1     | 1     |       |       |       |       |         |         |

d) Zeichnen Sie den Zustandsgraphen des Automaten. Denken Sie dabei an die duale Zustandskodierung. Kennzeichnen Sie die Zustandsübergänge (Pfeile) durch die zugehörigen Werte von X und Y.

e) Angenommen, das Schaltwerk befindet sich zum Zeitpunkt  $t_0$  im Zustand 1 ( $Q_1=0,\ Q_0=1$ ). In welchem Zustand befindet sich das Schaltwerk nach fünf Taktzyklen T, also zum Zeitpunkt  $t_1=t_0+5\cdot T$ , wenn X=1 und Y=1 ist??

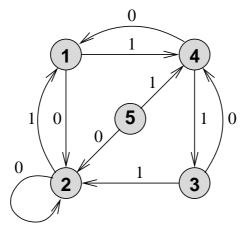

### Schaltwerkssynthese

Gegeben ist der unten abgebildete Zustandsgraph. Gesucht ist ein Schaltwerk mit JK-MS-FFs, welches diesen Zustandsgraphen realisiert.

Die binäre Variable an den Kanten des Zustandsgraphen stelle eine Eingangsvariable X dar, über die das Schaltwerk von außen in seinem Verhalten gesteuert werden kann.

- a) Wieviele FFs werden mindestens benötigt? Begründen Sie Ihre Antwort kurz.

- b) Ermitteln Sie die Zustandstabelle des Schaltwerks. Benutzen Sie dabei so viele don't-care-Einträge wie möglich. Verwenden Sie eine duale Zustandscodierung, d.h. es gelte  $z = (Q_n \dots Q_0)_2$ .

- c) Geben Sie möglichst kurze Ansteuergleichungen für die Eingänge der Flipflops an. Verwenden Sie KV-Diagramme zur Vereinfachung.

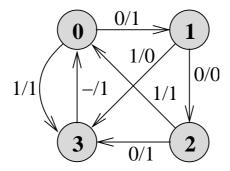

## ${\bf Zustandsgraph}$

Gegeben ist der folgende Zustandsgraph eines Mealy-Automaten, wobei sich das Ausgangssignal auf den jeweiligen Folgezustand bezieht.

- a) Warum beschreibt dieser Zustandsgraph einen Mealy-Automaten?

- b) Zeichnen Sie einen äquivalenten Zustandsgraph mit gleicher Funktion als Moore-Automat.

#### Entwurf einer Steuerung

Bei einer seriellen Datenübertragung wird zur Sicherung ein fünfstelliger sogenannter 2-aus-5-Code benutzt, dessen Kodeworte in der folgenden Tabelle aufgelistet sind.

|   | $x_4$ | $x_3$ | $x_2$ | $x_1$ | $x_0$ |

|---|-------|-------|-------|-------|-------|

| 0 | 1     | 1     | 0     | 0     | 0     |

| 1 | 0     | 0     | 0     | 1     | 1     |

| 2 | 0     | 0     | 1     | 0     | 1     |

| 3 | 0     | 0     | 1     | 1     | 0     |

| 4 | 0     | 1     | 0     | 0     | 1     |

| 5 | 0     | 1     | 0     | 1     | 0     |

| 6 | 0     | 1     | 1     | 0     | 0     |

| 7 | 1     | 0     | 0     | 0     | 1     |

| 8 | 1     | 0     | 0     | 1     | 0     |

| 9 | 1     | 0     | 1     | 0     | 0     |

Zu entwerfen ist ein Schaltwerk, das die beim Empfänger bitseriell einlaufenden Kodeworte (Bit  $x_0$  zuerst) auf Übertragungsfehler hin untersucht. Um bei einem erkannten Fehler eine Wiederholung des fehlerhaft übertragenen Kodewortes zu initialisieren, soll der Fehler nach dem vollständigen Einlaufen einen Takt lang durch ein Ausgangssignal F=1 angezeigt werden.

- a) Wieviele Eingangs- und Ausgangsvariablen besitzt das Schaltwerk? Definieren Sie die Eingangs- und Ausgangsvariablen. (2P)

- b) Entwickeln Sie das Zustandsdiagramm dieses Schaltwerks. (15P) Beachten Sie dabei den folgenden Hinweis:

Das Zustandsdiagramm stellt einen binären Entscheidungsbaum dar, dessen Verzweigungen sich durch die Bitstellenentscheidungen ergeben. Jede einlaufende Bitstelle erzeugt eine weitere Verzweigung, so dass bei 5 Bit grundsätzlich 1+2+4+8+16=31 Zustände darzustellen wären. Der Zustandsraum vereinfacht sich erheblich, wenn man berücksichtigt, dass es bei einem fünfstelligen 2-aus-5-Kode nur genau

$N = \binom{n}{w} = \frac{n!}{w!(n-w)!} = \binom{5}{2} = \frac{5 \cdot 4}{1 \cdot 2} = \frac{20}{2} = 10$

Kodeworte mit zwei Einsen gibt. Für diesem Fall sollten Sie auf einen Entscheidungsbaum mit 14 Zuständen kommen.

c) Überprüfen Sie das unter b) entwickelte Zustandsdiagramm auf äquivalente Zustände hin, und reduzieren Sie wenn möglich den Zustandsraum. (8P)

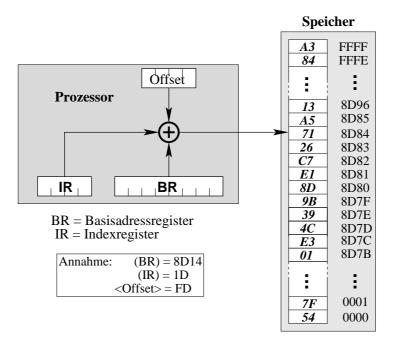

#### Prozessor

Ein 8-bit-Mikroprozessor besitze ein 16-bit-Basisadressregister BR und ein 8-bit-Indexregister IR. Bei einer indizierten Adressierung werde die effektive Adresse EA eines Operanden durch die Addition des Inhalts von IR und eines im Befehl angegebenen Offsets zum Inhalt von BR gewonnen. Dabei werden die Inhalte von BR und IR als vorzeichenlose ganze Zahlen, der Offset als vorzeichenbehaftete ganze Zahl im Zweierkomplement aufgefasst. Das folgende Bild verdeutlicht die Bildung der EA und zeigt einen Ausschnitt der Speicherbelegung zum aktuellen Zeitpunkt.

Das Indexregister IR verfüge über die Möglichkeit der automatischen Modifikation (autoinkrement/autodekrement) um die Werte n=1,2,3,4 sowie die Möglichkeit der Skalierung mit den Faktoren m=1,2,4.

Der Inhalt des Basisregisters BR sei wie im obigen Bild gezeigt 8D14 und der Offset FD (Hinweis:  $FD|_{16} = -3|_{10}$ ), der Inhalt des Indexregisters IR sei 1D.

Geben Sie an, welche effektive Adresse EA bei indizierter Adressierung mit Offset und Skalierung mit n=2 und m=4 angesprochen wird und wie diese Adresse dabei gebildet wird.

Führen Sie diese Betrachtungen für die drei Fälle

- (1) keine automatische Modifikation,

- (2) automatische Predekrementierung und

- (3) automatische Postdekrementierung

durch. Geben Sie ferner an, welches Datum aus dem Speicher gelesen wird und welchen Wert das Indexregister IR nach der Befehlsausführung hat.