# Optimization of cluster on-chip architectures

# Master thesis

Frank Thiele

10.07.2013

Matriculation number: 8082758 Supervisor: Prof. Dr. Jörg Keller

# Table of content

| 1.    | Introduction                                                | 1 |

|-------|-------------------------------------------------------------|---|

| 2.    | Intel's Single-Chip Could Computer                          | 5 |

| 3.    | Optimization of the merge sort algorithm for the Intel SCC  | 9 |

| 3.1.  | Merge sorting                                               | 9 |

| 3.2.  | Mapping approach1                                           | 3 |

| 3.3.  | Optimization approach1                                      | 5 |

| 4.    | Optimization of the Intel SCC for the merge sort algorithm2 | 3 |

| 4.1.  | Motivation                                                  | 3 |

| 4.2.  | ILP model adaptations2                                      | 3 |

| 4.3.  | Tile and memory controller addressing29                     | 9 |

| 4.4.  | Optimizer selection                                         | 1 |

| 4.5.  | Optimization                                                | 3 |

| 4.5.2 | 1. The idea                                                 | 3 |

| 4.5.2 | 2. Cooling function                                         | 4 |

| 4.5.3 | 3. Neighbor selection                                       | 6 |

| 4.5.4 | 4. When to stop                                             | 7 |

| 5.    | Execution results and analysis                              | 9 |

| 5.1.  | Optimization with 4 MC4                                     | 1 |

| 5.2.  | Optimization with 6 and 8 MC5                               | 5 |

| 5.3.  | Certain model configurations59                              | 9 |

| 5.4.  | Mirrored configuration69                                    | 9 |

| 5.5.  | Lookout into further optimizations8                         | 0 |

| 5.6.  | Critical view into annealing8                               | 0 |

| 6.    | Investigation of further algorithms8                        | 1 |

| 6.1.  | Tiled-MapReduce                                             | 1 |

| 6.1.2 | L. The ILP model                                            | 3 |

| 6.1.2 | 2. Results and analysis                                     | 1 |

| 6.1.3 | <ol> <li>Non-mirrored annealing results</li></ol>           | 9 |

| 6.2.  | Mesh communication10                                        | 1 |

| 6.2.2 | 10. The ILP model                                           | 2 |

|       |                                                             |   |

| 6.2.2 | 2. Parameter tuning                                         | 1 |

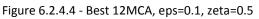

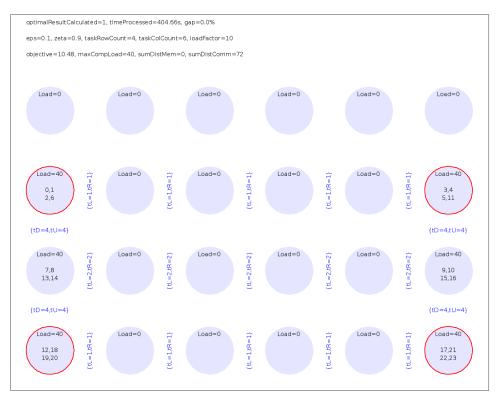

| 6.2.4.    | Results and analysis | 119 |

|-----------|----------------------|-----|

| 7. Con    | clusion              | 135 |

| Reference | ces                  | 137 |

| Abbrevia  | ations               | 139 |

| Eigenstä  | ndigkeitserklärung   | 141 |

# 1. Introduction

This work covers the domain of many-core computing research. The computer industry and scientists all over the world are developing multi-core systems and adapted software for them in order to reach even higher performance figures with the increasing number of cores on a single processing system. This can easily be seen when buying a new PC or laptop. At least 2 cores are the minimum this device should have in order to support a sensible performance for the demanding multimedia applications. This trend also reached the graphic card market years ago. Nvidia and ATI improve their graphic card performance nowadays rather by doubling, tripling or quadrupling the count of so called shader units than by increasing the frequency or jump prediction. This is required for most of the high end computer games and simulators to make them run at acceptable frame rates. So the achievements of many-core research have already reached the consumer market.

Today, the performance per processing unit has become less important as the speedup is mainly generated by more units than by faster ones. There are several reasons for this change of minds. The rise of the temperature caused by higher frequencies is one of the major factors. The thermal design power of the single-core CPU "Pentium 4 HT 550" (2004) is about 115 Watt. This is quite much and hard to cool - especially as energy saving optimizations of that time were much worse compared to today's ones. But this CPU offered a clock rate of 3.4 GHz. Current CPUs like the "Intel i7-2700K" operate at comparable frequencies but with 4 or more cores and tend to consume less power. The increased number of cores and internal improvements make this CPU much faster than factor 4 in several benchmarks.

The challenge for software developers of high performance applications (e.g. computer games or big data tools) therefore became even higher. It is pretty complex to implement highly efficient but still correct parallel algorithms that make full use of all cores of the processing units the system offers. Of course, compiler and library developers put a lot of effort into extensions that are easier and saver to use. However, to develop a correct and fast parallel program is and will be a challenge for all software developers. This becomes even more obvious when taking a look at a typical server setup with several multi-core CPUs. For such configurations NUMA (non-uniform memory access) awareness becomes the key factor for efficient parallel software to maintain a high performance even when scaling the system. If not taken into consideration it might happen that by adding more cores to a process its performance slows down.

This work focuses on a many-core research processer from Intel, the so called SCC (Single-Chip Cloud Computer). It offers 48 cores placed on a single die. As the definitions of many and multi-core systems tend to differ from one author to another (some say at least 50 cores, others say many more than 16, see also [9]), this work defines the Intel SCC as many-core system. Each core of the Intel SCC is connected to an on-chip mesh network and can use this to communicate with other cores in a very fast way. With respect to external memory access the Intel SCC is a NUMA system as it uses 4 memory controllers. Each memory controller is responsible for 12 cores. The performance of the memory access is a function of the distance between the core and the memory controller. So to develop high performance software for this device is quite a big challenge.

Figure 1.1 - Intel SCC die, 45nm technology, Intel.com

The purpose of this work is to investigate the influence of the memory controllers to a set of selected parallel algorithms that are executable on the Intel SCC. As the distance of the controllers to the cores is a crucial point, the placement of them on the Intel SCC die is taken a deeper look at. The original configuration is compared against a number of alternatives. This comparison is possible as for each algorithm a mathematical model with several cost factors is created. The model assumes the algorithm to consist of several tasks that run in parallel. The way those tasks are mapped to cores tends from being very inefficient to very promising. The best result based on the cost factors is the optimal one. This optimization is done by Integer Linear Programming (ILP) - a mathematical algorithm that can solve a number of inequalities that make up the model to optimality.

As already explained the best result depends on the cost factors. This work considers 3 cost factors: Memory distance for core to memory communication, communication distance for core to core communication and the computational load per core that expresses how many tasks are mapped onto a single core. As several factors are used the weight between them has a strong impact on the outcome of the optimization. For example if the weight of the computational load factor is very small, the weight of the distance costs becomes higher which typically results in a high load for some cores and no load for others. With respect to a real life system this would mean to have a processor with very fast cores but a pretty slow communication network. There it doesn't make sense to use all cores as the communication of the intermediate results to another core is too expensive. The weight factors are varied in order to simulate the most likely conditions that might occur when running an implementation of the algorithm on a real many-core system.

The number of possible locations where the four memory controllers can be attached to is very high for a 48 core cluster. To avoid the calculation of the optimal placement of tasks for each memory controller configuration, Simulated Annealing is used in order to decrease the trial count drastically. As the optimization run for a single placement may take up to several hours depending on the complexity of the model, this approach is absolutely necessary. In addition to the location changes the number of controllers is also varied. Within this work the best memory controller locations for 4, 6, 8 and 12 memory controllers are investigated.

The result of the optimization runs is that the basic Intel SCC setup is not the overall winner which is kind of astonishing as one might think that the Intel labs are having a strong focus on performance. But as this die is only a proof of concept for future many-core CPUs and intended to be used by scientists only, the not optimal placement can be seen as a good challenge to further think about better designs for algorithms that circumvent such performance disadvantages by intelligent communication structures. A possible reason for this uncommon choice might be that the Intel designers decided to put the memory controllers to the non-optimal position with respect to performance because of more important hardware requirements like a short distance to die edges or less electrical interferences to and from other components of the die.

Another and also expected result is that the addition of more memory controllers speeds up the performance of all algorithms. This can be explained best with the average distance of a node to a memory controller. The more memory controllers are given, the less the average distance of each core to the external memory becomes.

This work is organized as following. The next chapter introduces the Intel SCC and its properties in more detail. Chapter 3 explains the first algorithm to be optimized which is merge sorting. It gives some links to papers that are the base for this thesis and demonstrates the ILP model used there. Chapter 4 is about the adaptation of this model to make it possible to vary the memory controller count and location. Also, the application of Simulated Annealing can be found there. The succeeding chapter 5 summarizes the results of the optimization runs for the merge sort model. Within this chapter the optimization is first done using the whole cluster and then for performance reasons only using a quarter of it. Chapter 6 applies all the ideas of chapter 3 to 5 to two further algorithms and compares their results to the previous ones. The first algorithm is Tiled-MapReduce and the second one is a mesh communication network.

# 2. Intel's Single-Chip Could Computer

The challenge for programmers and researchers today is to experiment with many-core systems to generate solution for current and future problems faster and more efficiently than ever before. This research became more important in the last years due to the challenge of still being able to double the performance of a CPU in the typical 18 months period (referring to David House). The "doubling of performance every 18 months" phrase is based on Moore's law who predicted the doubling of the transistor numbers on an integrated circuit every two years and David House who combined this with the increasing speed of the transistors itself. In 2010 Intel announced the end of that predicted development at the end of 2013 [2]. They stated that the transistor density can then only be doubled every three years. The currently most promising way forward back to the old performance development seems to be a combination of the classical more and better transistors together with improved logic on the CPU (e.g. branching prediction) and the addition of more cores on a single die. So by implementing such CPUs and finding an effective high-performance implementation of important and commonly used algorithms one can find the way making sure that future software can still become quicker and quicker the same way we're used to since decades.

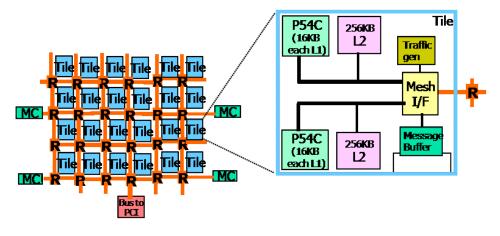

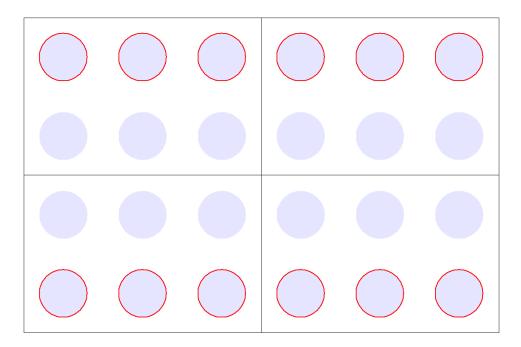

The Intel SCC ("single-chip cloud computer") is a many-core system even though its core count is not that high. Predecessors of it have already included up to 80 cores [11]. It is a so called cluster on-chip system and was published in the end of 2009 as prove of concept (POC) for researchers. It offers 48 computing cores which are placed on the die within 24 tiles. The tiles are arranged in a mesh of 4 rows and 6 columns. In this context a tile can be seen as a modern multi-core CPU with two cores. The tiles are connected using a packet based mesh network. Each core is attached to a L1 cache of size 32KiByte (16/16 for data/code) and L2 cache of 256KiByte. An interesting thing about the caching is that there is no synchronization between the caches of different cores. This needs to be implemented by software means. The advantage of this decision beside less power consumption and less hardware complexity is the enforcement of message passing as this performs much better than the communication using the external memory. The cores itself are pretty old fashioned (IA32 P54C, published in 1993) and therefore a significant speedup compared to modern CPUs can only be reached by heavily making use of all the 48 cores. The die is manufactured in 45nm technology and can consume up to 125W of power.

The routing of data packages between the tiles is done using X-Y-routing which is implemented by routers on the die. The main memory access and node to node communication is controlled by the mesh interface unit (MIU) that sends requests to and handles requests from the router. The core to core communication itself uses an extra on-tile buffer of size 16KiByte which is called MPB (message passing buffer). The buffer is read and write accessible from all cores of the mesh.

The memory attached to the die is connected to 4 routers only. So the tiles next to the router are closest to the memory. Those tiles are located on the left and right side in each second row (seen from top to down).

Figure 2.1 - Top level tile architecture, Intel.com

The address width of the system is 36Bit so that up to 64GiByte of RAM can be used by all cores. This address space is referred to as system address space. A core itself can only address 4GiByte within the core address space of 32Bit. The MIU is responsible for translating local core addresses to and from global system addresses.

Figure 2.2 - The Intel SCC on a special main board, Intel.com

The programming and general control of the Intel SCC is done by a management console PC (MCPC). The "Rocky Lake system FPGA" connects the Intel SCC system with a normal PC by a PCIe link. The FPGA can also act as I/O hub. This enables services like disk or Ethernet access. So one can create a cluster of Intel SCC hosts or offer very fast algorithm implementations via a web service to the local organization. In the picture 2.2 the FPGA is located under the small fan, the Intel SCC die under the big fan and the PCIe and Ethernet port can be found

where the external devices are typically connected to. There is also a so called "Board management controller" (BMC). This runs a Linux system on a little ARM CPU and offers services like boot strapping the FPGA. It can be connected to via Telnet or SSH (see [10]). On the Intel SCC itself a special Linux distribution is running, too.

# 3. Optimization of the merge sort algorithm for the Intel SCC

The next chapters introduce an Intel SCC adaptation of the merge sort algorithm (see [4]) found by a group of researchers from the FernUniversität Hagen (Germany) in cooperation with the Linköping University (Sweden).

The first sub chapter briefly summarizes the algorithm and the succeeding ones describe the required changes and retrieval of an optimized mapping of the algorithm onto the Intel SCC cores.

# 3.1. Merge sorting

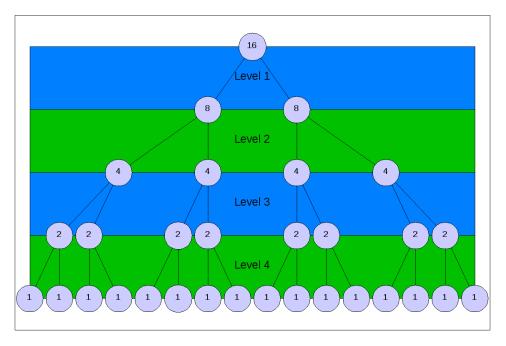

The goal of merge sorting is to sort a number of sortable objects, e.g. ordinary integers. In the case of binary merge sorting this is done by dividing the original block of data into sub blocks of half the size (binary). If the new blocks have the size 2, the sorting is trivial and can be done directly. Otherwise, the new blocks are again divided. Two sorted blocks are then merged together based on the sorting order into one block of their aggregated size.

This approach leads to a merge tree - in case of binary merge sorting to a binary merge tree that is illustrated with the following graph. A merge task represents a node of the tree. In the figure, the merge tasks are not painted. Only the blocks to be sorted are displayed.

Figure 3.1A - Binary merge tree with 4 levels

In a classical non-parallel way the algorithm is implemented recursively. Using Perl, the code could look like shown in the following code block:

```

sub mergeSort {

my @numbers = @ ;

my $count = scalar @numbers;

if ($count > 2) {

my $half = int($count/2);

my @leftNumbers = @numbers[0..$half-1];

my @rightNumbers = @numbers[$half..$count-1];

my $sortedLeftNumbers = mergeSort(@leftNumbers);

my $sortedRightNumbers = mergeSort(@rightNumbers);

my @sortedNumbers = ();

for my $value (@sortedLeftNumbers) {

while (defined $sortedRightNumbers[0] && $value > $sortedRightNumbers[0]) {

my $rightValue = shift @sortedRightNumbers;

push @sortedNumbers, $rightValue;

}

push @sortedNumbers, $value;

}

push @sortedNumbers, @sortedRightNumbers;

return @sortedNumbers;

}

elsif ($count == 2) {

if ($numbers[0] > $numbers[1]) {

return (

$numbers[1],

$numbers[0],

);

}

else {

return @numbers;

}

}

return @numbers;

```

Figure 3.1B - Perl example of sequential merge sorting

For the classical parallel execution the merge tree becomes important because the merge sort algorithm is then split into phases based on the levels of the tree. Within a phase one level of the merge tree is processed.

In case of a 4 level binary merge tree (so 16 elements to be sorted), the fourth level is the first one to be processed. All 16 blocks of size one are sorted into 8 blocks of size 2. This is done in parallel by 8 workers. The next phase can be supported by 4 workers that process in parallel the 8 sorted two-element blocks into 4 sorted blocks of 4 elements each. This is done by merging the two sets together. The next level is level 2. Here, the 4 blocks are merged into 2 blocks by 2 workers. And the last phase handles level 1. Here, only a single worker merges the 2 blocks of size 8 into a single sorted result block of size 16.

There exist some approaches to further use all cores even though the number of blocks within a phase is smaller than the worker count divided by 2 (for a binary tree).

In order to reduce the number of levels and the overhead in the first merges (little number of objects to be merged), the merge sort algorithm can be extended to sort the highest levels in the first phases using another sorting algorithm. This becomes important later when taking a look at the Intel SCC adaptations. An interesting point of the "complete" merge tree is the fact that even for small object numbers there are normally less workers than leafs so that the nodes of the leaf level are not processed in parallel. The same applies for the higher levels where more destination blocks than workers are present.

If one assumes p workers, then the normal parallel merge sort tree that is processed levelwise has p leafs so that all nodes of the leaf level can be processed in parallel. For each leaf there are 2 blocks of sortable objects in the binary case. This makes 2\*p blocks of unsorted objects. Those blocks need to be sorted before starting to merge them in parallel. In the best case each block fits into the workers local memory (e.g. cache). If this requirement is fulfilled, a worker can sequentially sort (e.g. quick sort) a block without accessing the external memory (excepting the initial read from and final store to memory). After all 2\*p blocks are sorted in parallel (in two phases) the parallel merge sort can start at the leaf level where all p workers merge 2\*p sorted blocks into p sorted blocks.

If the 2\*p blocks are too large for the local memory of each processing unit, then one can normally not avoid accessing the external memory. How this can be achieved anyway is described in the following. The merge tree is further extended until for each leaf the size of its input blocks is less or equal than the local processing memory. Then the merge tree has m leafs and m is greater than p so that there are not enough workers to process the new leaf level in parallel. The way forward leads to the introduction of sub merge trees starting at the highest level with less or equal than p nodes (the "regular leaf level"). The leaf count of each sub merge tree must be less or equal then p (otherwise, the sub merge tree must be extended/split, too). Then every sub merge tree can be sorted by p workers in parallel as described above. The leaf nodes of the sub merge trees are sorted locally in parallel. Once all sub merge trees are processed, the regular leaf level can be processed in parallel.

# 3.2. Mapping approach

In [3] one can find in detail how the merge sort algorithm was efficiently adapted and mapped to the Intel SCC. The following gives an overview of the ideas and the solution found.

Implementing the parallel execution explained in chapter 3.1 is not very promising for one reason - the memory access performance. The memory bandwidth of the Intel SCC is limited, especially the write performance is very poor (less than 11MiByte per second and per core, see [5]). As the phase-wise execution requires the data to be fully read and fully written back into a new memory area, this approach is not feasible.

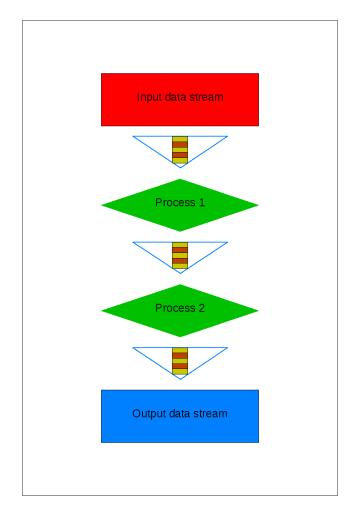

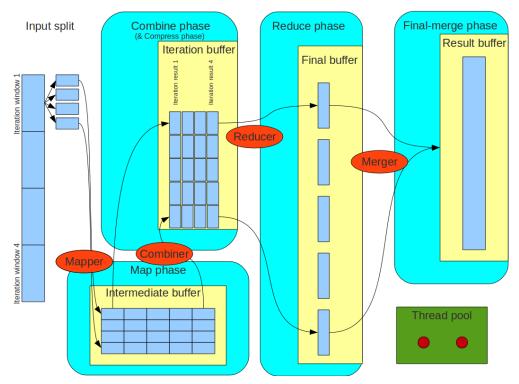

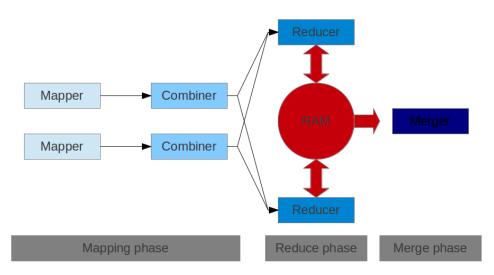

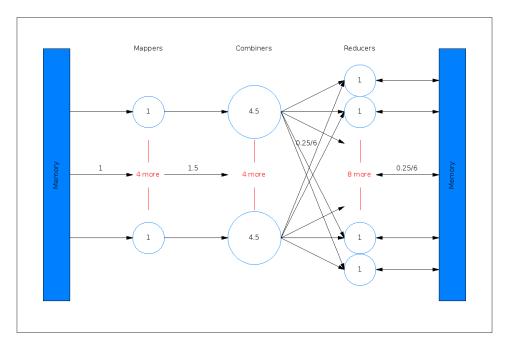

The idea was to use pipelining which has the advantage that it can make full use of the much faster core to core communication. Pipelining describes the processing of data by a number of stream processing units in series. Stream processing means that an input data stream can be separated into logical blocks and each block can be processed by the processor independent of the next data block. The processing result can then be streamed in blocks to the next processing unit which can directly consume the data in parallel to its input units generating the next data blocks. This is referred to as pipelining. The following graphic shall demonstrate this from a high-level perspective.

Process 1 reads the data stream block wise and outputs the resulting stream in blocks to process 2 that further processes the results and generates an output data stream, too.

This processing schema has the advantage that no external memory is required between the processing units. All data is holed in caches and registers. On the Intel SCC this means that the mesh network can be used to transfer the stream data from node to node directly. The main memory is so only accessed once when reading the unsorted data from and once again when writing the sorted data back to memory. This puts the memory bottleneck only to the border of the pipeline making the overall pipeline much faster as the waiting time for the memory operations is not aggregated any more from node to node.

The pipeline processes were then defined to be the merge tasks of the merge tree. In level 4 of figure 3.1A there are 8 merge tasks. The result of those can be streamed to the 4 merge tasks of level 3 and so on.

Depending on the level the merge task is defined for, it has more or less work to do. For each level, the sum of the work load is equal. Assuming now the idea to map the tasks equally (with respect to load) to the cores of the Intel SCC, one would require a 48 level merge tree where all tasks of a level are mapped to a single core. This makes up a total of 281e12 tasks. As each task requires some management data this way is not feasible.

The way forward was then to cut the Intel SCC into 4 parts each being attached to one of the four memory controllers. So, each part has 2 rows and 3 columns of tiles, so 6 tiles or 12 cores in total. This can be used to map two independent 6 level trees with 63 tasks each to the tiles/cores of the divided cluster. The merge sort of the resulting 12 merge trees so results in 12 sorted sets of data. This can then be sorted separately using a non-pipelined merge sort.

But what level shall be put to which core? Does it make sense to put tasks of different levels to a single core? The answers to these questions are given in the next chapter.

As indicated in chapter 3.1 one can presort the input in order to reduce the size of the tree. As the 48 level merge tree requires too many tasks, the presort needs to be done for the pipelined merge sort, too. The paper describes quick sort as the algorithm to be used to presort the data for the highest level. This means for the leaf level that instead of sorting 2 elements 2 sorted sets of n elements are to be merged. Assuming a 6 level merge tree the number of tasks of the leaf level is 32. This means that 64 sorted sets of equal size are to be generated by quick sort.

# **3.3. Optimization approach**

Chapter 3.2 explained that pipelining the merge sort tasks is better than simply mapping them onto the Intel SCC cluster nodes and leaving the data transfer unchanged. How pipelining can be done as good as possible and what the optimal mapping of each task to a node is will be explained in this chapter.

The basic idea is to design a mathematical model describing the influence of different cost factors on the overall performance. This model is then optimized and the best solution found which represents the Pareto optimal mapping of tasks to nodes can then be implemented. By using a mathematical optimization program called integer linear programming one can use a number of linear equalities and inequalities to describe and solve the model. There are a number of implementations (or solvers) for such models available, e.g. CPLEX and Gurobi. These solvers also support floating point variables and partly non-linear inequalities. Both have their own modeling language but there exists a framework called AMPL that is capable of mapping a common language into both models so one can easily compare different solvers with each other. The work [3] showed that for the required model Gurobi is much faster than CPLEX.

Integer linear programming (ILP) tries to minimize or maximize an object function. The object function depends on variables that are bounded by linear constraints that are typically formulated using inequalities. So by finding constraints for the cost factors having an influence on the performance, one can define an object function summing up those costs. The goal is to find the minimum or maximum value of the object function called the objective. In our example this means to be able to see the perfect mapping of tasks onto the cores for which the total costs are minimized.

The following cost functions have been found in [3]:

- Maximum computational load: This defines the highest load per node. This makes sense as the node with the highest load requires the most time to finish its tasks.

- Memory distance costs: [4] revealed that the distance of a node to the memory controller has significant impact on the read and write performance. The faster the data can be transferred, the faster the sorting can be finished. So by summing up the distances of the tasks mapped to an Intel SCC node that communicate with the main memory, one can approximate this influence.

- Node communication costs: As for the memory distance, the latency from node to node has an influence on the data throughput. This latency becomes higher with higher distances. So by summing up the distances of tasks communicating with each other (father and its sons), one can approximate the influence.

As the relative share of the 3 different cost functions depends on the implementation and hardware capabilities it is unknown. So one needs to make assumptions and formulate those using factors. This leads to the introduction of epsilon (eps) and zeta. Both have a floating point value between 0 and 1. Eps defines the relation between the maximum computational load and the distance costs. This means that the 2 distance related cost factors are grouped together. If eps is 1 then the computational load is the only relevant cost factor. If eps is 0 then only the distance is taken into account. Zeta defines the relation between memory and node to node distance costs. If zeta is 1 then the memory distance costs are the only relevant distance cost factor. Of course, the results of an optimization with two different eps

and zeta values can be very different. Testing those different results shows up what eps and zeta values are more realistic for a given system. But this is not part of this work.

An important idea of the work was to define co-tasks. Co-tasks exist for the root node and for the leaf tasks of the merge tree. The co-tasks are used to model the calculation of the distance from the root and leaf tasks to the memory controllers. Due to pipelining the root and leaf tasks are the only tasks that communicate with the external memory.

The following AMPL model presents the result of the mentioned thoughts. It does not take into consideration that only one quarter shall be looked into. It assumes the full Intel SCC and is presented here as it is the base for chapter 4. It contains some fixes to the original one used in [3].

```

option show_stats 1;

option omit_zero_rows 0;

option omit_zero_cols 0;

option eexit 1; #bail out on exit

option solver gurobi_ampl;

option gurobi_options 'outlev=1 timing=1';

```

Figure 3.3.1 - AMPL model for full cluster optimization - part 1

The first code block is about setting run time options that affect the output and behavior of the solver. As Gurobi has been found to be a fast solver, it is bound here as the solver to be used when running the model.

```

param k integer;

param b integer;

set V = 1..(b**k-1)/(b-1);

set Vinner = 1..(b**(k-1)-1)/(b-1);

set Vext = 0..(2*(b**k)-(b**(k-1))-1)/(b-1);

set Vco = ((b**k-1)/(b-1)+1)..(2*(b**k) - (b**(k-1)) -1)/(b-1);

set Vleaf = (b**(k-1)-1)/(b-1)+1..(b**k-1)/(b-1);

set B = 1..b;

```

Figure 3.3.2 - AMPL model for full cluster optimization - part 2

The pipelined merge sort model has some parameters. Two of them are "k" and "b". "k" represents the levels of the tree. "b" represents the forking factor. It is 2 in all further chapters what means the tree is always binary. So each father task has two sons. Both parameters are of type integer.

The introduced parameters are then used to define so called sets. Sets are comparable to arrays and one can iterate over them. The sets defined here are used later. The syntax is related to the programming language Perl where a list of all numbers from 1 to 10 is generated with the expression "(1..10)".

The set "V" defines the set of all tasks belonging to a normal merge tree, starting with the root task 1 and ending with the last leaf task. The other "V\*" sets are extending the task set V or form a subset of it or are at least related to V. "Vinner" contains all the tasks of "V" having sons. This means that leaf tasks are not part of this set. "Vext" contains all tasks of "V" plus the co-tasks of the root and leaf tasks. "Vco" contains the co-tasks of the leaf tasks. So "Vco" is a subset of "Vext" but not of "V". "Vleaf" contains only leaf tasks. "Vleaf" plus "Vinner" together form "V".

And the last set defined is "B" which is holding the set of links of an anonymous father to is sons. For the case "b=2" each father can have 2 sons. So "B" contains the (input) link 1 and 2.

```

param NRows integer;

param NCols integer;

set Rows = 1..NRows;

set Cols = 1..NCols;

param secondMIC binary;

```

Figure 3.3.3 - AMPL model for full cluster optimization - part 3

The first two parameters describe the Intel SCC cluster layout. "NRows" holds the row count and "NCols" holds the column count of the tile cluster. The single cores of each tile are not modeled. Derived from the parameters the sets "Rows" and "Cols" are defined and contain an entry for each row respectively column of the cluster.

The last parameter "secondMIC" is also about the Intel SCC configuration. This is a flag (so of type binary) expressing whether or not the rightmost Intel SCC cluster column is attached to memory controllers. This flag was introduced to experiment with other memory controller settings and is normally set to 1 (true).

```

param eps in [0,1.0];

param zeta in [0,1.0];

param work {1..(b**k-1)/(b-1)} in [0,1.0];

```

Figure 3.3.4 - AMPL model for full cluster optimization - part 4

The remaining merge sort parameters are given here. The meaning of eps and zeta has already been discussed. They are defined as floating point variables between 0 and 1.

The "work" parameter is defined as array of type floating point. It contains the work or load per task. The task definition is the same as for the set "V". This means for each normal task (no co-tasks) an entry exists. This also implies that a co-task has no load. It is just used to model the memory distance of its corresponding root or leaf task. The addressing of tasks in the work and some other later defined arrays works by numbering the tasks like in the "V" set and using those numbers as array indexes. The zero index of the arrays is normally in contrast to most programming languages 1 instead of 0.

The root entry "work[1]" typically has the load 1. The entry value of its two sons 1 and 2 is typically 0.5 as the number of objects (not blocks) received from the father is the same as the sum of the objects the sons have sorted. This means the load per tree level is equal. This is made sure by the executor program filling this parameter array.

```

var x{v in Vext, row in Rows, col in Cols} binary;

var quad{v in V, q in 1..NRows} binary;

```

Figure 3.3.5 - AMPL model for full cluster optimization - part 5

Now, variables are introduced. Those contain the equality and inequality argument values and are changed by the optimizer so that the objective function is improved.

The first variable is "x". It is a variable set and models the mapping of each task onto the cluster tiles. This means that "x" must be a three dimensional array. The first dimension carries the task index, and the other two the row and column number of the cluster. The tasks to be mapped are all tasks including co-tasks. This is why "Vext" is given. The mapping

value is a flag. If it is 1 the task is mapped to the given row and column. If it is 0 it is not mapped to the given row and column of the cluster.

The "quad" variable set helps to bind the co-tasks to the same quadrant as the corresponding task.

```

var sumDistComm in interval[0.0,10000.0];

var sumDistMem in interval[0.0,10000.0];

var maxCompLoad in interval[0.0,10000.0];

minimize obj:

eps*maxCompLoad

+ (1-eps)*(1-zeta)*sumDistComm

+ (1-eps)*(zeta)*sumDistMem;

```

Figure 3.3.6 - AMPL model for full cluster optimization - part 6

Here, the cost variables are defined. The objective function named "obj" is stated here. It combines the cost variables with the weight factors eps and zeta. The minimum value (keyword "minimize") of the object function shall be found and represents the objective.

```

subject to MappingOnce {v in Vext}:

sum {row in Rows, col in Cols} x[v,row,col] = 1;

```

```

Figure 3.3.7 - AMPL model for full cluster optimization - part 7

```

The constraints are called "subjects" in the AMPL modeling language. Here the first can be seen. It is about the constriction that each task must be mapped exactly to one tile. Expressed with linear equations this means that for each task (see subject definition "v in Vext") the sum of all entries (meaning all positions in the cluster expressed by row and column number) of the mapping variable set "x" is equal to 1. So there is no unmapped or multiple times mapped task.

```

subject to DefineMaxCompLoad { row in Rows, col in Cols }:

maxCompLoad >= sum{v in V} work[v] * x[v,row,col];

```

Figure 3.3.8 - AMPL model for full cluster optimization - part 8

The variable "maxCompLoad" is set here. Therefore, for each tile (row and column, see subject definition) the mapping variable set "x" is checked whether a normal merge task is mapped to it. This "fact" (can be 0 or 1) is weighted by multiplying it with the load for that task ("work" array). The single results are summed up by "sum{v in V}". Please note that the sum is then only set as an upper bound to "maxCompLoad" (">="). But as the objective function shall be minimized, the "greater or equals to" becomes effectively an equals ("="). This is typical for ILP solvers.

```

subject to notinthisrow0even { r in 1..NRows/2 }:

sum { c in Cols } x[0,2*r,c] <= 0;

subject to notinthisrow0odd { r in 1..NRows/2 }:

sum { c in 2..NCols-secondMIC } x[0,2*r-1,c] <= 0;

subject to notinthisrowcoeven { v in Vco, r in 1..NRows/2 }:

sum { c in Cols } x[v,2*r,c] <= 0;

subject to notinthisrowcoodd { v in Vco, r in 1..NRows/2 }:

sum { c in 2..NCols-secondMIC } x[v,2*r-1,c] <= 0;</pre>

```

Figure 3.3.9 - AMPL model for full cluster optimization - part 9

Those subjects are all about co-task mapping constraints. The first two force the root co-task (index 0) to be mapped only to the first and last column of each odd row (counting starts with 1 at bottom) of the cluster. There, the memory controllers are attached to the router of the so addressed tile. This becomes a little bit more complicated by the parameter "secondRow" defining whether the last column contains a memory controller or not. If it is 0, the root task cannot be mapped to the last column. "Cannot be mapped" is expressed as "x[0, row, column] <= 0". All entries that are not touched by the sum around this expression are not bounded and can therefore contain the root task (if not further restricted by later subjects).

The other two subjects are equal to the first two subjects but here it is about the leaf cotasks. The difference can be found in the task index and in the subject header that now also contains the leaf set "Vco" to iterate over.

In general, one can see that using the "NRows" parameter one can influence the memory controller count as for each odd row at least one memory controller exists.

Figure 3.3.10 - AMPL model for full cluster optimization - part 10

This code block fills the quad variable set. It aims on setting the entry "quad[v, z]" to 1 for a normal task v if the task v is mapped to the quadrant z. z is a value from 1 to "NRows" where:

- z is 1 for row 1 and 2 and for the left row part [column 1 to NCols/2 (integer division)]

- z is 2 for row 1 and 2 and for the right row part [column NCols/2+1 to NCols]

- z is 3 for row 3 and 4 and for the left row part [column 1 to NCols/2 (integer division)]

- z is 4 for row 3 and 4 and for the right row part [column NCols/2+1 to NCols]

- ..

The mathematical expression for z can be found in the subjects. If there are 4 rows, then there are 4 quadrants. 2 additional "quadrants" can be found for 6 rows and so on.

The first subject defines the upper bound and the second the lower bound. The first therefore depends on the task mapping variable set "x". If a task is not mapped to the quadrant, the entry shall be less or equal to 0 (as binary this means equal to 0). If the task is mapped to the quadrant, the entry can be less or equal to "1". And the second subject is

comparable to the subject "MappingOnce". It requires the "quad" variable set to contain exactly one non-zero entry for each task of "V".

The next figure shows where the quad variable set is used.

```

subject to force1 { memcrow in 1..NRows/2, memccol in 0..1, v in Vleaf }:

x[ v+b**(k-1), memcrow*2-1, memccol*(NCols-1) + 1 ]

<= quad[v,memcrow*2-1+memccol];

subject to force2 { memcrow in 1..NRows/2, memccol in 0..1 }:

x[ 0, memcrow*2-1, memccol*(NCols-1) + 1 ]

<= quad[1,memcrow*2-1+memccol];</pre>

```

#### Figure 3.3.11 - AMPL model for full cluster optimization - part 11

Subject "force1" restricts the leaf co-tasks (leaf task index + number of nodes in last level) to be mapped to the same quadrant as its corresponding leaf task. The second subject applies the same rule to the root co-task.

Figure 3.3.12 - AMPL model for full cluster optimization - part 12

The node to node communication distance calculation is calculated in two phases. In the first phase, for each task "child(u, i) :=  $b^{(u-1)+i+1}$ " it is stored from which row "r1" to which row "r2" and from which column "c1" to which column "c2" it is sending data. "i" is the child link number (see set "B"). "u" is the father node that receives the data from its children. The information is stored as a flag in the variable sets "yh" (horizontal) and "yv" (vertical). The mapping of each task to a tile and the function "child(u, i)" to get the communication path are the input parameters for the derivation. The derivation works as following:

- If a son of "u" is mapped to row "r1" and "u" is mapped to row "r2", then the entry of "yv[child(u, i), r1, r2]" is greater or equal 1. This means that the son of u is sending from row r1 to row r2 data.

- If a son of "u" is mapped to row "r1" and "u" is not mapped to row "r2", then the entry of "yv[child(u, i), r1, r2]" is greater or equal 0.

- If a son of "u" is not mapped to row "r1" and "u" is mapped to row "r2", then the entry of "yv[child(u, i), r1, r2]" is greater or equal 0.

- If a son of "u" is not mapped to row "r1" and "u" is not mapped to row "r2", then the entry of yv[child(u, i), r1, r2] is greater or equal 0 (normally -1, but binary values are allowed only).

"Greater or equal" becomes "equal" due to the global minimization of the object function. The same applies for the "yh" variable set.

The node to node communication exists only for the destination tasks of the set "Vinner". Excluded are the leaf tasks as they have no children other than co-tasks that send data to them.

The second phase of the node to node communication distance calculation is to deduce the distance from the communication information variable sets. This can be seen in the figure 3.3.15.

The leaf tasks have no children. But they get their data from the leaf co-tasks and so from the memory. The root task sends its data via the root co-tasks to the memory. As already stated the co-tasks are just a helper to model the distance to memory. The co-tasks are mapped to the tile that is closest to the memory controller. If one now derives the distance from co-task to its corresponding task and sums this up, the memory distance is the result. The same approach as for node to node communication can be used here. The first phase of that is shown in the following two figures. The last phase can be found in figure 3.3.16.

Figure 3.3.13 - AMPL model for full cluster optimization - part 13

The source of the memory communication in level 1 is the root. The receiver is task 0, the root co-task. So as like as in figure 3.3.12 the communication information is stored in "yh" and "yv".

Figure 3.3.14 - AMPL model for full cluster optimization - part 14

The sources of the memory communication in the level k are the leaf co-tasks sending data to the leaf tasks in level k. So as like as in figure 3.3.12 the communication information is stored in "yh" and "yv".

Figure 3.3.15 - AMPL model for full cluster optimization - part 15

Having stored what task is sending data from one place to another, the information is evaluated in this subject for all tasks that use a pipelined communication. If the task is sending data from row "r1" to "r2" then the positive difference of "r1" and "r2" is weighted by multiplication with the load of the source. This weights the sent data with its distance. The overall sum represents the weighted node to node communication distance.

```

subject to defineSumDistMem:

sumDistMem =

# root task to co-root task

sum {i in B, r1 in Rows, r2 in Rows}

yh[1, r1, r2] * abs(r2 - r1) * work[1]

+ sum {i in B, c1 in Cols, c2 in Cols}

yv[1, c1, c2] * abs(c2 - c1) * work[1]

# co-leaf task to leaf task

+ sum {v in Vleaf, i in B, r1 in Rows, r2 in Rows}

yh[v+b**(k-1), r1, r2] * abs(r2 - r1) * work[v]

+ sum {v in Vleaf, i in B, c1 in Cols, c2 in Cols}

yv[v+b**(k-1), c1, c2] * abs(c2 - c1) * work[v];

```

Figure 3.3.16 - AMPL model for full cluster optimization - part 16

Similar to before, this subject is about distance calculation. But this time it is about the root and leaf tasks and their distance to the off-chip memory.

# 4. Optimization of the Intel SCC for the merge sort algorithm

### 4.1. Motivation

The Intel SCC has been designed to allow developers and scientists to test their theoretical models and ideas on hardware that is likely to be commonly used in the next years. Unfortunately, this hardware is fixed. One cannot predict how an implementation would behave if the amount of cores is doubled, what impact it would have if the mesh network performance is changed or the network itself becomes a hierarchical network with core and sub networks.

In order to investigate the influence of some of the possible parameters the following chapters explain how the merge sort AMPL model can be changed and used to determine the effect of varying those parameters.

## 4.2. ILP model adaptations

In contrast to the original model where the memory controller positions are fixed to 2 respectively 4 positions ("secondMIC" parameter) for 4 rows, the new model has been extended to allow the memory controllers to be placed freely. With the new model, the memory controller location and count can be configured. If required, the memory controllers can even be placed within the inner area of the board. As the preceding model was already capable of configuring different row and column numbers, there is no upgrade required.

The extensions also include some changes with respect to memory distance calculations which are required due to the relaxation of the memory controller locations.

The following figures show the AMPL model bit by bit.

```

#include "tree-scc-map-latency-mem4-v3.define"

option show_stats 1;

option omit_zero_rows 0;

option omit_zero_cols 0;

option eexit 1; // bail out on exit

option solver gurobi_ampl;

option gurobi_options GUROBI_OPTIONS; // This parameter is defined in the *.define

file

```

Figure 4.2.1 - Extended merge sort model - part 1

The initial option setup is equal to the chapter 3 model. The only difference is the C preprocessor directive "#include" that is parsed and interpreted before the model is run. It is used to automatically create dynamic code like a time limit after which the solver stops optimizing and returns the intermediate results.

```

param k integer;

param b integer;

set V = 1..(b^{*}k-1)/(b-1);

set Vinner = 1..(b^{**}(k-1)-1)/(b-1);

set Vext = 0..(2*(b**k)-(b**(k-1))-1)/(b-1);

set Vco = ((b^{*}k-1)/(b-1)+1)..(2^{*}(b^{*}k) - (b^{*}(k-1)) -1)/(b-1);

set Vleaf = (b^{**}(k-1)-1)/(b-1)+1..(b^{**}k-1)/(b-1);

set B = 1...b;

param NRows integer;

param NCols integer;

set Rows = 1..NRows;

set Cols = 1..NCols;

param eps in [0,1.0];

param zeta in [0,1];

param secondMIC binary;

param rootweight in [0,1];

param wscale in [0,b];

param work {1..(b**k-1)/(b-1)} in [0,1];

```

Figure 4.2.2 - Extended merge sort model - part 2

This is equal to chapter 3 and requires no further explanation.

```

param memoryControllerCount integer >= 1;

set memoryControllers = 1..memoryControllerCount;

param memoryControllerMapping {group in memoryControllers, r in Rows, c in Cols};

param rootGroup;

```

#### Figure 4.2.3 - Extended merge sort model - part 3

This code block is new and presents the implementation of the variable memory controller count and location. It is realized with the parameter set "memoryControllerMapping" that describes to what tile a memory controller (or better: router of the tile) is placed to. The parameter "memoryControllerCount" and the corresponding set "memoryControllers" have also been introduced for that. The parameter set "memoryControllerMapping" contains for each memory controller (called group here) a two dimensional array that has a "1" at exactly that tile entry where the memory controller is connected to. This must be made sure by the caller of the model defining the content of the parameters.

Another parameter defined here is the "rootGroup" parameter. This will be explained later.

```

var x{v in Vext, row in Rows, col in Cols} binary;

var yh{v in Vext, r1 in Rows, r2 in Rows} binary;

var yv{v in Vext, c1 in Cols, c2 in Cols} binary;

```

#### Figure 4.2.4 - Extended merge sort model - part 4

The meaning of those variable sets has already been described in chapter 3 and requires no further explanation.

```

var sumDistComm in interval[0.0,10000.0];

var sumDistMem in interval[0.0,10000.0];

var maxCompLoad in interval[0.0,10000.0];

minimize obj:

eps*maxCompLoad

+ (1-eps)*(1-zeta)*sumDistComm

+ (1-eps)*(zeta)*sumDistMem;

```

Figure 4.2.5 - Extended merge sort model - part 5

This is equal to chapter 3 and requires no further explanation.

```

subject to MappingOnce {v in Vext}:

sum {row in Rows, col in Cols} x[v,row,col] = 1;

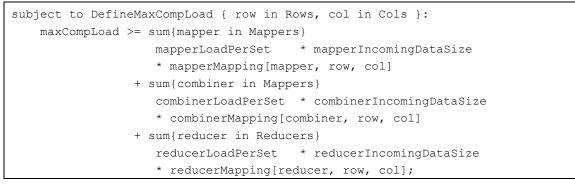

subject to DefineMaxCompLoad { row in Rows, col in Cols }:

maxCompLoad >= sum{v in V} work[v] * x[v,row,col];

```

#### Figure 4.2.6 - Extended merge sort model - part 6

This is equal to chapter 3 and requires no further explanation.

```

// co-tasks are mapped to the memory controller nodes.

subject to zeroTaskIsMappedToMemoryControllerNode {col in Cols, row in Rows}:

#ifdef USE_ROOT_GROUP

x[0, row, col] <= memoryControllerMapping[rootGroup, row, col];

#else

x[0, row, col] <= sum {memGroup, row, col];

#emoryControllerMapping[memGroup, row, col];

#endif

```

Figure 4.2.7 - Extended merge sort model - part 7

Here, the root co-task location restriction is modeled depending on whether the "USE\_ROOT\_GROUP" feature is enabled or not (via C preprocessor directive, so defined by caller). The first runs of the model revealed a significant performance improvement of the model run time by permanently setting the root co-task to a dedicated memory controller node. This fixation is now configurable and can be turned off if required. So if the "USE\_ROOT\_GROUP" feature is enabled, the root co-task (0) is forced to a certain memory controller tile (to be more precise: to the router of that tile). In this case, the parameter "rootGroup" is evaluated. If the feature is not enabled, this parameter is ignored and the subject is just about mapping the root co-task to exactly one of the configured memory controller tiles.

The quad variable set has been removed as it further complicates the model.

```

subject to leafCoTasksAreMappedToMemoryControllerNode {v in Vco, col in Cols, row

in Rows}:

x[v, row, col] <= sum {memGroup in memoryControllers}

memoryControllerMapping[memGroup, row, col];</pre>

```

```

Figure 4.2.8 - Extended merge sort model - part 8

```

The constraint of mapping the leaf co-tasks to the memory controller tiles is implemented here. This is implemented differently than in chapter 3 as here is no rule known any more to express the memory controller positions (before: every odd row contains 1 or 2 memory controllers). Now the "memoryControllerMapping" parameter set is summed over for each tile and controller. If for a certain tile the entry of a memory group is 1 then the leaf co-task can be mapped to that tile. Otherwise this is not allowed.

Figure 4.2.9 - Extended merge sort model - part 9

This can also be found in chapter 3. Both subjects are about the first part of the node to node distance calculation.

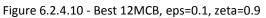

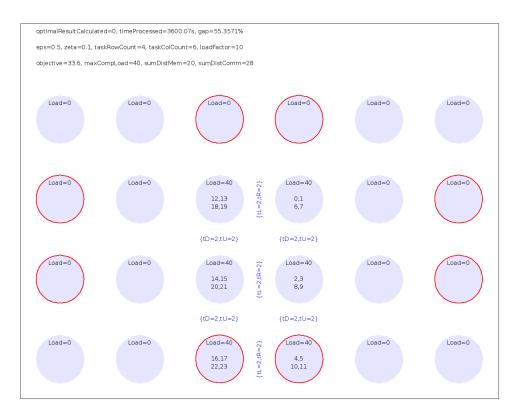

Figure 4.2.10 - Extended merge sort model - part 10

This figure and the next one are equal to chapter 3. They are about the first part of the distance to memory calculation.

Figure 4.2.11 - Extended merge sort model - part 11

Figure 4.2.12 - Extended merge sort model - part 12

The final subject that calculates the sums of the node to node communication costs is equal to the one of chapter 3. No changes were required. The same applies to the last figure below where the distance to memory is finally aggregated.

Figure 4.2.13 - Extended merge sort model - part 13

# 4.3. Tile and memory controller addressing

The location of the memory controllers can now be changed freely. In order to make clear to what tile the memory controller is attached to without using an illustration an addressing schema is required.

This can be done by giving each tile an address. Within this work the tiles are named using one of the following two addressing schemes:

- The tile in the top left vertex is named "1,1" or "0". The left tile in the second row is addressed with "2,1" or "6" assuming a column count of 6.

- The first address contains two numbers separated by a comma:

- The first number is the row index of the cluster (counting from top to down, starting with 1).

- The second number is the column index of the cluster (counting from left to right, starting with 1).

- The second address is the linear transformation of the first address type. It can be calculated as following: "(rowIndex 1) \* columnCount + columnIndex 1".

- The left tile in the second row is addressed with "2,1" or "6" assuming a column count of 6.

- The right tile in the second row is addressed with "2,6" or "11" assuming a column count of 6.

- And so on...

Applied to the Intel SCC this means:

- There are tiles from "0" (top left vertex) to "23" (bottom right vertex).

- The tiles "6", "11", "18" and "23" have a memory controller attached to their router.

If the memory controller of the bottom right vertex "23" ("4,6") is moved to the top right position, then the new address of it would be "5" or "1,6".

## 4.4. Optimizer selection

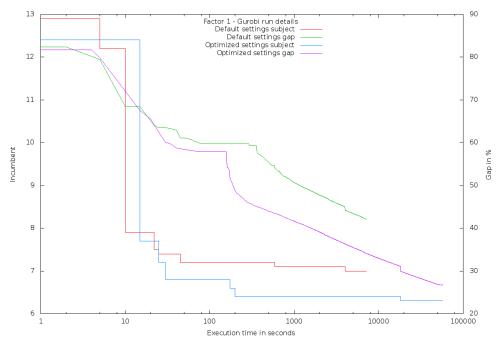

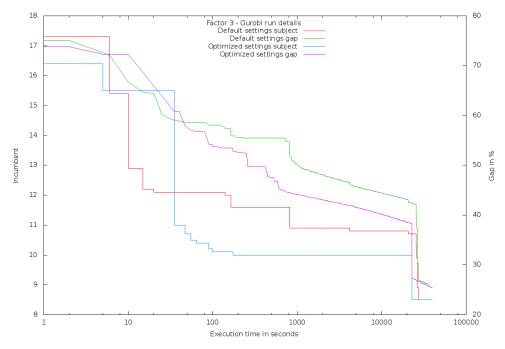

The selection of the optimizer is crucial with respect to the time within the optimal solution of a model is found. At least this is the first idea one could have when trying to find a good solver for the merge sort model. But finding the optimal solution is not the only important property that should be considered when comparing different optimizers and versions. The approach used to find the best model is explained in detail later. For now, it is enough to say that the best configuration of a huge set of possible memory controller positions for the model is approximated. Inherent to this principle is not to find the best but a good local solution which is described in the next chapters. With respect to that one can define the perfect optimizer for the merge sort model to be the one with the fastest and best candidate. That means the intermediate results are good enough compared to a given value and do not necessarily need to be optimal.

As already stated in the previous chapters Gurobi is a very fast solver for the merge sort model. This is why this work will not consider other optimizers. Instead of that, only different versions of Gurobi are compared against each other. As the model is written in the description language of AMPL only the published versions of the combination of AMPL and Gurobi are tested. There are many more Gurobi standalone versions which cannot be considered here.

The following table represents the results of 6 runs for 4 different versions of AMPL with Gurobi. Each run uses a certain memory controller configuration. As each run for a given configuration behaves very much equal when repeated only one trial is used. The first 4 digits of the "setup" column define the controller positions, the last one the root memory controller index ranging from 1 to 4 (as 4 memory controllers are used).

| VERSION | SETUP        | VALUE                | TIME     | 5%    | 3%    | 1%    | 0%    |  |

|---------|--------------|----------------------|----------|-------|-------|-------|-------|--|

| 4.6.1a  | 0_1_6_12_1   | 1.1875               | 1800.01s | 1762s | 1762s | 1800s | 1800s |  |

| 5.0.0   | 0_1_6_12_1   | 1.1875               | 1800.06s | 73s   | 76s   | 1368s | 1368s |  |

| 5.0.2   | 0_1_6_12_1   | 1.2109375<br>(+2.0%) | 1800.48s | 77s   | 82s   | 82s   | 109s  |  |

| 5.1.0   | 0_1_6_12_1   | 1.203125<br>(+1.3%)  | 1800.02s | 19s   | 19s   | 46s   | 1591s |  |

|         |              |                      |          |       |       |       |       |  |

| 4.6.1a  | 0_1_6_12_2   | 1.1875               | 1384.13s | 55s   | 64s   | 1095s | 1095s |  |

| 5.0.0   | 0_1_6_12_2   | 1.203125<br>(+1.3%)  | 1800.03s | 15s   | 19s   | 65s   | 92s   |  |

| 5.0.2   | 0_1_6_12_2   | 1.203125<br>(+1.3%)  | 1800.04s | 15s   | 20s   | 66s   | 93s   |  |

| 5.1.0   | 0_1_6_12_2   | 1.1875               | 997.41s  | 42s   | 42s   | 42s   | 53s   |  |

|         |              |                      |          |       |       |       |       |  |

| 4.6.1a  | 2_3_20_21_1  | 1.2421875            | 961.07s  | 60s   | 841s  | 889s  | 889s  |  |

| 5.0.0   | 2_3_20_21_1  | 1.2421875            | 888.92s  | 99s   | 785s  | 785s  | 839s  |  |

| 5.0.2   | 2_3_20_21_1  | 1.2421875            | 919.48s  | 63s   | 63s   | 851s  | 876s  |  |

| 5.1.0   | 2_3_20_21_1  | 1.25<br>(+0.6%)      | 1802.61s | 77s   | 80s   | 164s  | 164s  |  |

|         |              |                      |          |       |       |       |       |  |

| 4.6.1a  | 2_3_20_21_2  | 1.2421875            | 976.19s  | 53s   | 66s   | 123s  | 879s  |  |

| 5.0.0   | 2_3_20_21_2  | 1.2421875            | 934.65s  | 49s   | 97s   | 869s  | 884s  |  |

| 5.0.2   | 2_3_20_21_2  | 1.2421875            | 809.45s  | 43s   | 679s  | 765s  | 765s  |  |

| 5.1.0   | 2_3_20_21_2  | 1.2421875            | 982.21s  | 24s   | 850s  | 850s  | 850s  |  |

|         |              |                      |          |       |       |       |       |  |

| 4.6.1a  | 6_12_11_17_1 | 1.2734375            | 961.64s  | 106s  | 800s  | 800s  | 830s  |  |

| 5.0.0   | 6_12_11_17_1 | 1.3359375            | 1800.02s | 57s   | 57s   | 1546s | 1546s |  |

Table 4.4.1 - Results of a comparing run between different Gurobi versions

| VERSION | SETUP        | VALUE     | TIME     | 5%   | 3%    | 1%    | 0%    |

|---------|--------------|-----------|----------|------|-------|-------|-------|

|         |              | (+4.9%)   |          |      |       |       |       |

| 5.0.2   | 6_12_11_17_1 | 1.2734375 | 1179.37s | 705s | 1059s | 1113s | 1113s |

| 5.1.0   | 6_12_11_17_1 | 1.2734375 | 1414.19s | 141s | 141s  | 141s  | 157s  |

|         |              |           |          |      |       |       |       |

| 4.6.1a  | 6_12_11_17_2 | 1.2734375 | 1264.88s | 38s  | 131s  | 131s  | 131s  |

| 5.0.0   | 6_12_11_17_2 | 1.2734375 | 1800.01s | 676s | 676s  | 743s  | 899s  |

| 5.0.2   | 6_12_11_17_2 | 1.2734375 | 1800.02s | 674s | 694s  | 694s  | 709s  |

| 5.1.0   | 6_12_11_17_2 | 1.2734375 | 929.40s  | 25s  | 35s   | 823s  | 905s  |

The intermediate values reached while running are displayed in the range columns, e.g. 38s in the 5% column means that after 38s the intermediate solution was within a 5% range of the final (but not necessarily optimal) solution of the run. Red markers show that the time limit of 30 minutes was hit. Green markers express that the value is the best of the current range. Orange markers are used to show that the range was hit faster than for the green ones but the overall result compared against is worse (see value column).

In order to compare the results against each other, the green and orange markers are summed up where green markers are weighted with the factor 1 and orange ones with 0.5. The overall winner out of that is Gurobi v5.1.0 with 10 points. The second winner with 9 points is version 5.0.0. The others have less than 7 points.

As the number of tests is pretty small and the weighting factors are kind of arbitrary the informational value can be questioned. But due to time limitations this should be acceptable.

#### 4.5. **Optimization**

In this chapter it shall be explained how the Intel SCC can be optimized. A precondition for an optimization is the knowledge about what can be changed in order to achieve better results at all. Therefore, the "setup" of the model to be optimized needs to be defined. This setup includes the definition of the hardware (cluster) and software (merge sort) parameters:

- hardware specific parameters

- memory controller count (4 for Intel SCC)

- o row count (4 for Intel SCC)

- column count (6 for Intel SCC)

- merge sort specific parameters

- o eps (weight of computation over communication costs)

- o zeta (weight of memory controller distance over node distance costs)

- k (number of merge tree levels)

- o work load per task

In principle one can now try to find the best result for a fixed setup by changing the hardware layout within the requirements of the setup. In this case, the memory controller positions are modifiable as only their count is defined. But running the model with all possible values takes too much time. For example for a model with 4 rows, 6 columns and 4 memory controllers there are  $4 \times 6 = 24$  positions where a memory controller can be placed. As there are 4 memory controllers the number of possible combinations is 24! / (20!\*4!) = 10626. This needs to be multiplied by 4 as for each combination the root co-task can be placed to one out of four controllers. In sum about 42k alternatives to be calculated. Assuming only very optimistic 100 seconds for each run would result in nearly 50 days of calculations.

Assuming that memory controllers can only be attached to the edges of the cluster the situation becomes more relaxed as for 16 possible locations only about 8.5 days of processing time are required. But this is still too much as the run needs to be done several times, e.g. for different eps and zeta values or to make sure that the result is really very good.

As running the model for all possible memory controller positions resulting from a given setup is unacceptable the following chapters describe one possible way to find good but not optimal solutions.

#### 4.5.1. The idea

The basic assumption is that the optimal configuration won't get much worse just by slightly changing the memory controller positions. This also applies to configurations of the setup that are not optimal. There is always a neighboring configuration B of A so that B is either as good as A or at least pretty close to A.

This does not automatically apply to the root controller node (where the root co-task is fixed to) for odd configurations. An odd configuration means here an odd memory controller distribution. But to make the optimization as easy as possible this can be accepted.

There are a number of optimization algorithms that could be used to find a good solution by searching them randomly and testing their neighborhood for even better values. One of

those is Simulated Annealing. Because of its easy application to the problem it has been chosen to find the optimal solution for a certain model setup.

Based on the idea of the controlled annealing of metal to minimize the occurrence of defects this algorithm uses a start temperature that cools down from iteration to iteration. Here, iteration refers to an optimization run that produces a specific result for the current configuration of the model setup. From iteration to iteration a neighbor of the current best configuration is selected and tested. The current best configuration is adapted if the current configuration is either equal or better than the current best configuration or if the probability p of the difference (to the current best) and the current temperature is higher than a randomly chosen value in the range of 0 and 1.

The further the annealing process progresses the lower the temperature and therefore the lower the chance to accept a worse configuration as the current best configuration becomes. The function of p is predefined as  $e^{-1}$ .

How to cool down, how to select a neighbor and when to stop is to be decided based on the specific model and its parameters that shall be optimized. The next chapters explain how this is done within this work.

### 4.5.2. Cooling function

Two options for the temperature cooling are investigated. The first is the linear temperature curve. It uses a start temperature and decreases this linearly with the current iteration number down to zero.

The second curve is based on a power function. It also uses this start temperature but decreases the temperature by dividing the start value by the current iteration number.

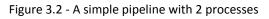

The following figure shall demonstrate both temperature functions inserted in the probability function e^(-diff/T). The first 3 examples in the legend use the power function, the last 3 ones use linear cooling. The difference is set to 0.1 as this corresponds to a difference in the subject of about 10 to 15% for the later introduced test. Early test runs of this work showed that the best result found was about 10 to 15% better than the result for the Intel configuration. So setting the value to 0.1 results in a probability function than can be interpreted as the likelihood that a very good configuration is replaced by a result that is just as good as the original Intel configuration.

Figure 4.5.2.1 - Graph displaying the probabilities for linear and power function based temperature annealing

One can see that the different options lead to two different behaviors for the same start temperature and a given difference. The linear function leads to steady changes for a long time whereas the power function represents the opposite - worse values become much earlier unacceptable. The higher the start temperature is set the higher the iteration count becomes for the same probability.

Experiments with a small statistic show that for the Intel SCC merge sort model the power function with temperature 8 (the second in the legend of above) delivers more frequently good results. The following table summarizes those tests. In this table the header is to be read like that: "P\_8" means that the power function is used with a start temperature of 8. "L\_7" means that the linear function is used with a start temperature of 7.

| Subject cluster | P_8 | P_16 | L_5 | L_7 |

|-----------------|-----|------|-----|-----|

| (1.12 - 1.15)   | 1   | -    | -   | -   |

| (1.15 - 1.18)   | 2   | -    | 3   | 1   |

| (1.18 - 1.20)   | 6   | 3    | 2   | 8   |

| (1.20 - 1.23)   | 1   | 5    | 3   | 1   |

| (1.23 - 1.26)   | -   | 2    | 2   | -   |

Table 4.5.2.1 - Results of annealing runs with both linear or power function and 2 different start temperatures,10 times each

The outcome of this experiment is normally only valid for the special model setup used (Intel SCC, eps=0.5, zeta=0.5, k=7). To speed up the required calculations, the algorithm and starting temperature is used anyway for all the other possible model setups having the same number of merge tree levels and memory controllers. This might have an impact on the degree of improvement over the original model. But as long as it can be improved this approach is acceptable.

If the mentioned parameters change the start temperature and iteration count are adapted by a little rule of thumb: "Higher parameter numbers require higher temperatures and more iterations". This fuzzy rule can be used and applied to generate a plot like in the previous figure to define the values. E.g. when running models with 6 memory controllers, the temperature is doubled to 16 but the iteration count is only increased by 50% to 60. For 8 memory controllers, the temperature is set to 24 and 70 iterations are used. In both cases, the function curve looks similar to the one with a start temperature of 8.

One other side note: By extending the memory controller count or the number of merge tree levels, more and more inequalities are to be considered by Gurobi. This typically requires a higher waiting time. The waiting time is also adapted with the same rule as for the temperature and iteration count and like there it cannot be considered as a perfect adaptation.

#### 4.5.3. Neighbor selection

The neighborhood of a configuration needs to be defined in order to select a neighbor of it. This can be done as following:

- A configuration X of a setup specifies the not already fixed model parameters. They are:

- The memory controller indexes MC[i] where i is a number between 1 and the memory controller count n. One such index is of the range [0, rowCount\*colCount-1] and represents the location of the memory controller.

- The root index r that describes to what memory controller the root co-task is attached. So r is a number between 0 and the memory controller count n minus 1 (see also chapter 4.2).

- The neighborhood N(X) of a configuration X can then be defined as the set of configurations for which a parameter value differs by maximum one unit compared to the same parameter of X.

- For the memory controller indexes and the root index this needs to be extended by the inclusion of the wrap around case: The difference between the maximum and the minimum value of a parameter is 1.

This definition includes the configuration in its own neighborhood.

There are two different parameters classes: Memory controller and root co-task index. For each class an array can be defined that contains all parameter values of a class.

Now one can define the neighbor selection with the following Perl program:

```

sub getNeighbors {

my ($parameterClassConfig, $probility, @valuesBefore) = @ ;

my $max = $parameterClassConfig->{Max};

my $min = $parameterClassConfig->{Min};

my @newValues = ();

my %valueIsUsed = ();

for my $currentValue (@valuesBefore) {

my $newValue = changeByOneUnit($probility, $currentValue);

$newValue = normalizeValue($newValue, $min, $max); # wrap around

while ($valueIsUsed{$newValue}) {

$newValue += $shallInc ? 1 : -1;

$newValue = normalizeValue($newValue, $min, $max); # wrap around

}

push @newValues, $newValue;

$valueIsUsed{$newValue} = 1;

}

return @newValues;

```

Figure 4.5.3.1 - Neighbor selection algorithm

The input of that algorithm is the parameter class configuration which contains the minimum and maximum values for the parameters and a probability value and the value array that represents the current configuration. The result contains a neighbor. This can be the same as the input configuration. The algorithm makes sure that the values of the array are distinct as it doesn't make sense to map two memory controllers to a single node. This function is used to get a neighbor for the two parameter classes. In the implemented final algorithm the probability value used is 0.7.

An optimization applied here is the avoidance of calculating a result for the same or a mirrored configuration twice. If this case is detected, the probability value used to change the neighbor values is increased to 1. Also, the neighbor selection uses another base configuration. Instead of using the current best result, the last neighbor found is then used to find the next neighbor. This maximizes the likelihood to get another unique neighbor and minimizes the calculation time.

#### 4.5.4. When to stop

The stop conditions for the annealing algorithm applied are:

- time limit for the whole optimization, e.g. 1 hour

- iteration limit, e.g. 30 iterations

The "better than X" limit has not been implemented as this could hide even better configurations.

#### 5. Execution results and analysis

Now the best model configuration for a model setup is tried to be found. The goal is to achieve better values than for the original Intel SCC model configuration. In theory, memory controllers (MC) can be placed anywhere around the cluster. This work simulates in this chapter a realistic hardware layout by putting the memory controllers to the edges of the cluster.

The tasks of the model are mapped to the tiles of the cluster and not to the cores of a tile. This is because otherwise the model would consist of 8 rows and 6 columns and some other changes related to memory controller placement would be required. As this leads to higher complexity and solution times, the calculation is simplified by just mapping tasks to tiles. More details can be found in chapter 3.2.

The following sub chapters describe the retrieval of a cluster configuration that is better than the Intel SCC. This is done in 4 different ways.

First, the best configuration is tried to be found using the full cluster. This has the disadvantage that because of the high complexity of a 24 level merge tree only a 7 level merge tree is used which results in a very poor load distribution. But the result is anyway interesting as the best memory controller setup found is an odd one. The second chapter 5.2 extends the chapter 5.1 by adding more memory controllers to the cluster and investigates the influence on the performance.

Chapter 5.3 is about the manual definition of the memory controller positions. The reason behind this manual selection is to find an even configuration that is better than the original Intel SCC configuration.

The next chapter uses another approach in order to get a perfect cluster usage. Therefore, chapter 5.4 introduces the mirrored configuration which automatically results in even memory controller configurations. The best results of the optimization runs for the merge sort model are shown here.

### 5.1. Optimization with 4 MC

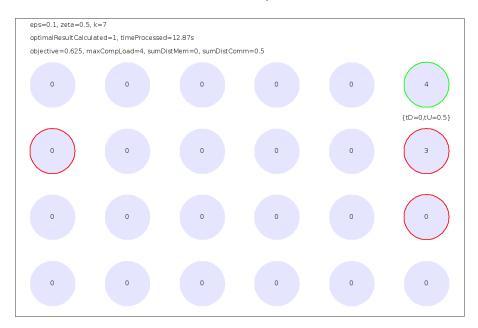

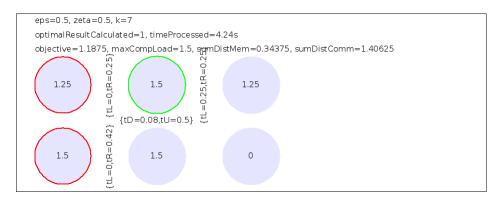

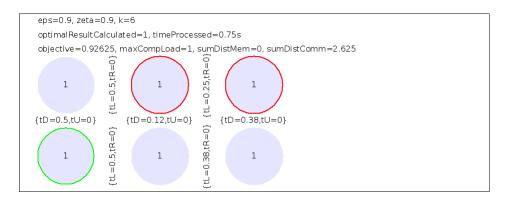

The following tables and figures present and summarize the output of two annealing runs. The following model setup was used: eps={0.1, 0.5, 0.9} and zeta={0.1, 0.5, 0.9}.

A1) communication costs predominate computation costs AND node distance costs predominate memory controller distance costs

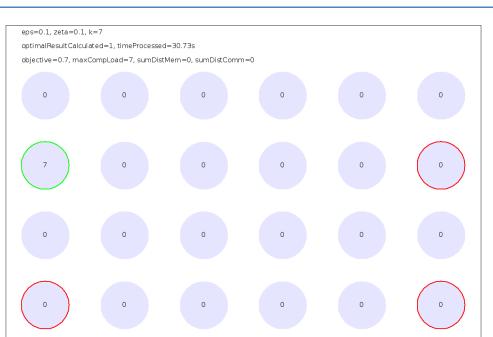

|                    | Subject | maxCompLoad | sumDistComm | sumDistMem |

|--------------------|---------|-------------|-------------|------------|

| Intel SCC          | 0.7     | 7           | 0           | 0          |

| Best configuration | 0.7     | 7           | 0           | 0          |

Table 5.1.A1 - results of eps=0.1, zeta=0.1

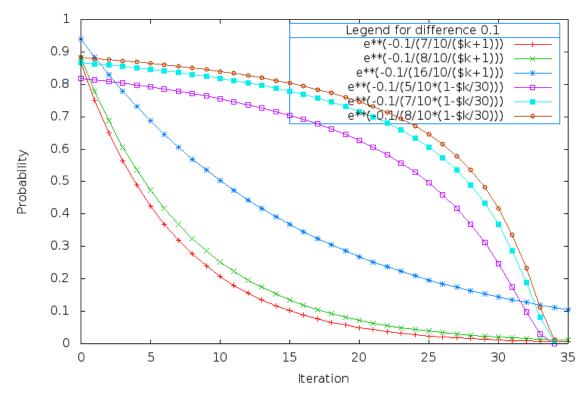

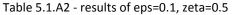

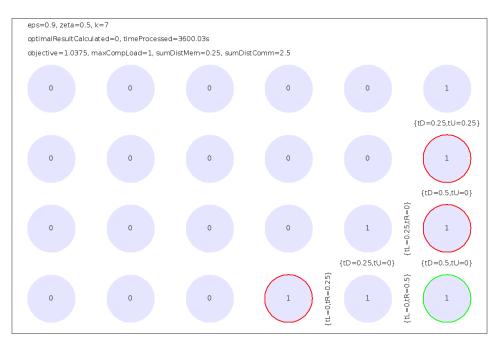

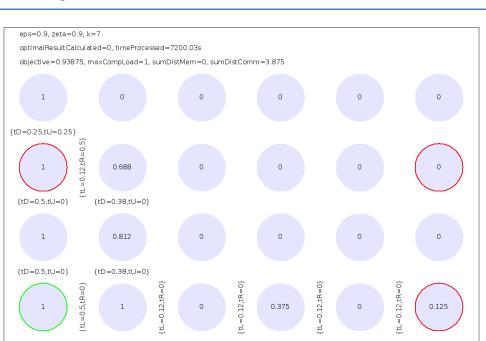

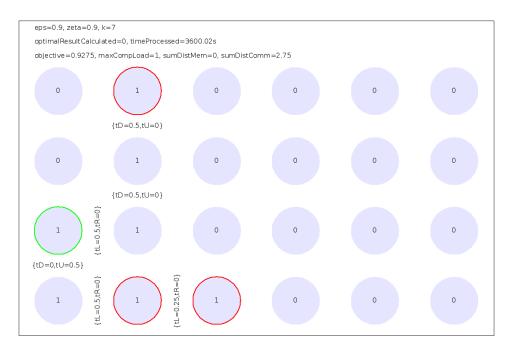

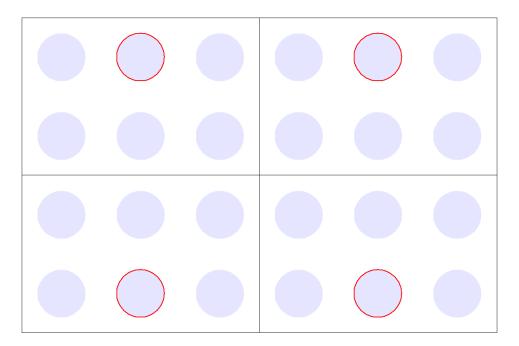

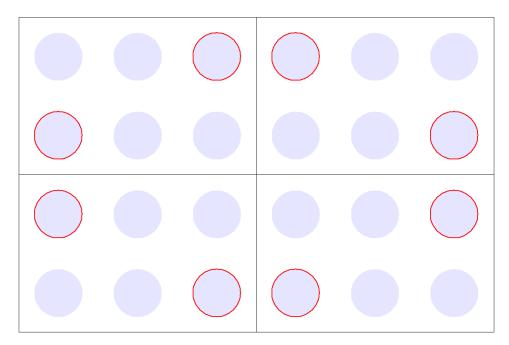

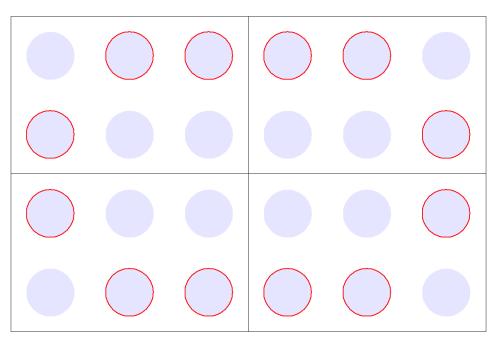

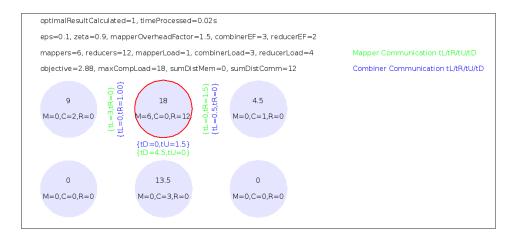

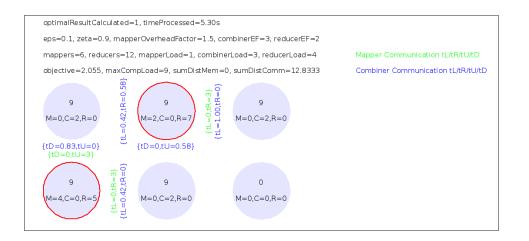

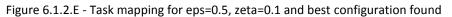

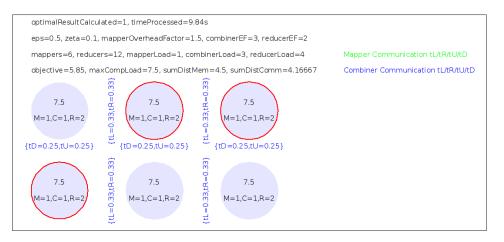

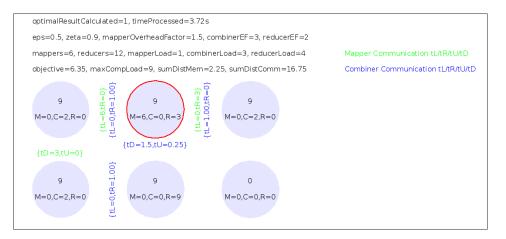

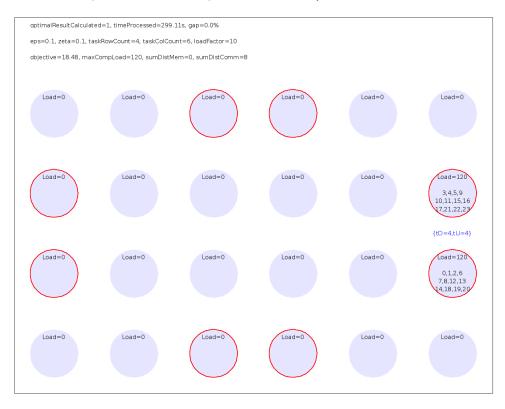

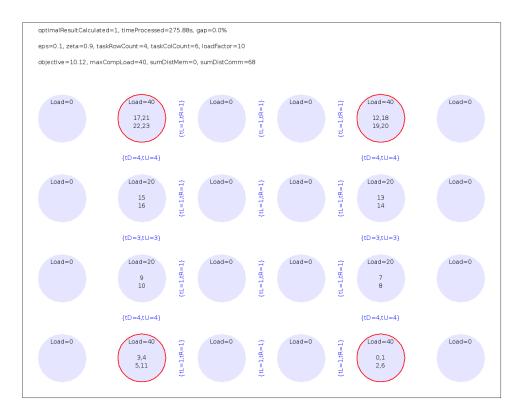

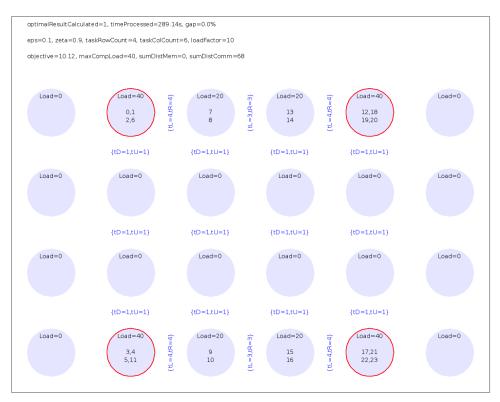

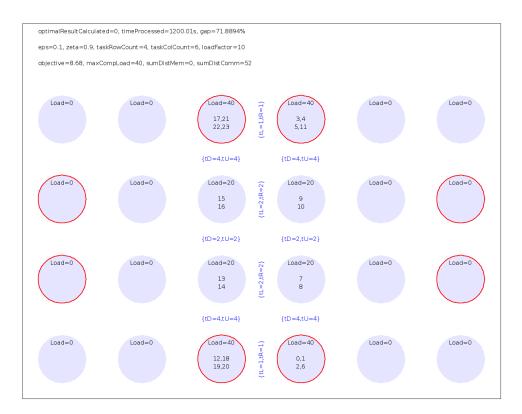

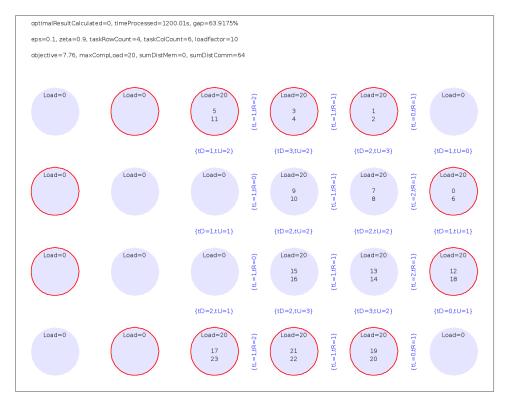

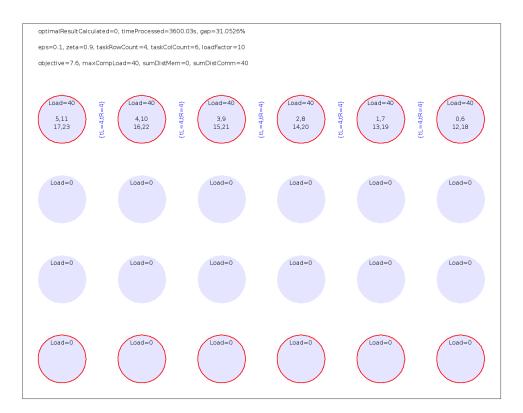

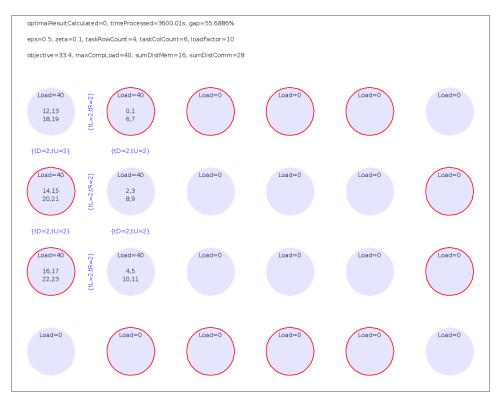

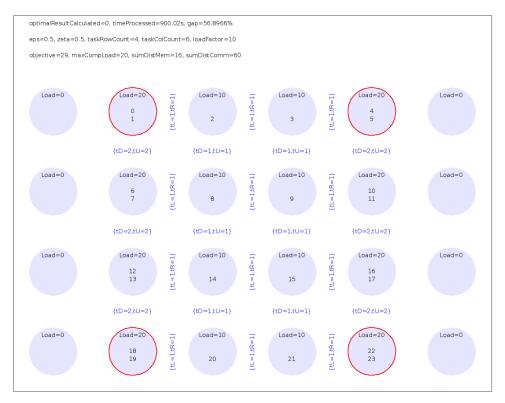

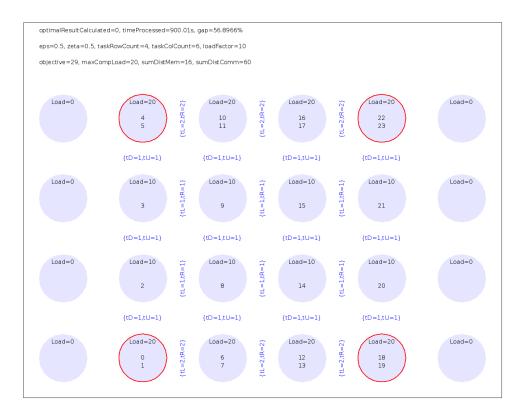

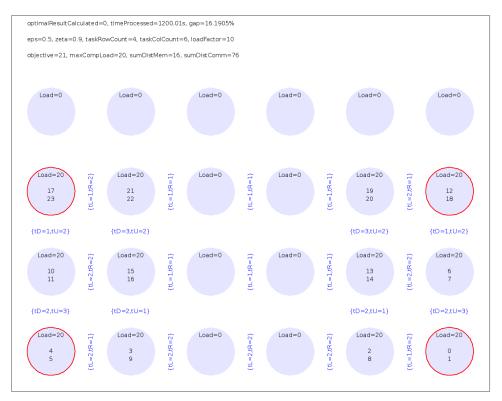

Figure 5.1.A11 - Intel SCC task and memory controller mapping

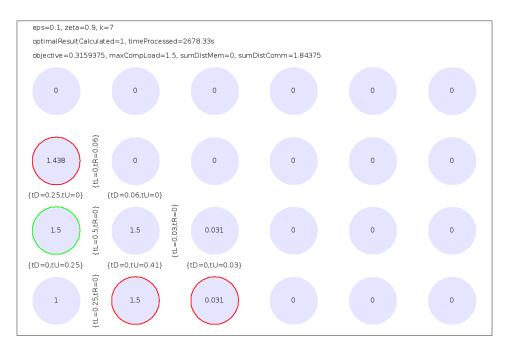

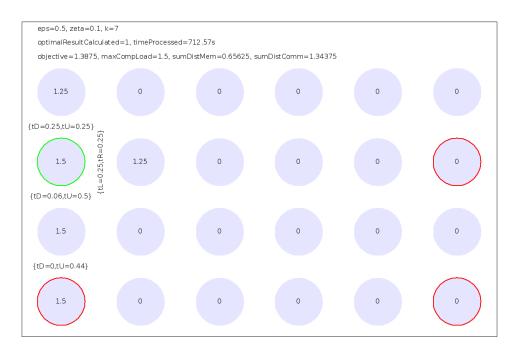

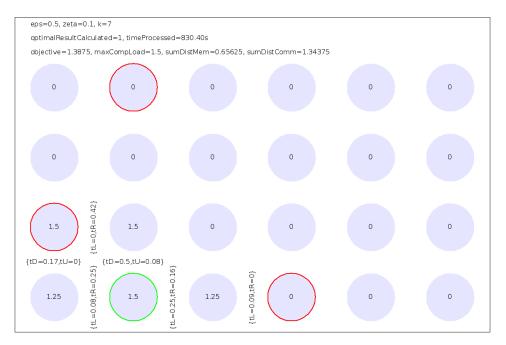

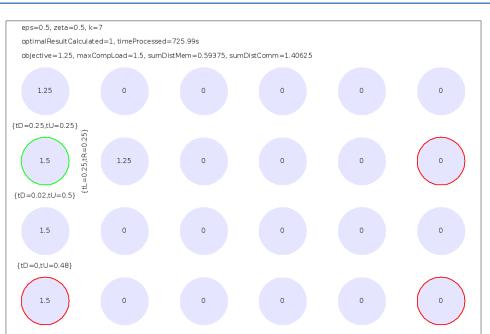

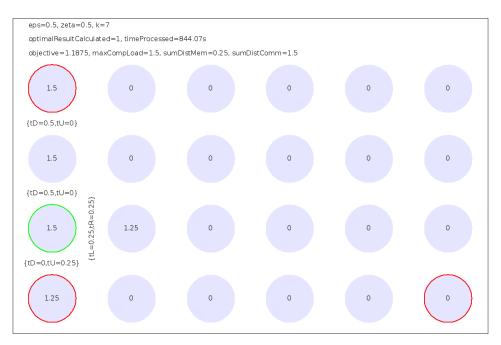

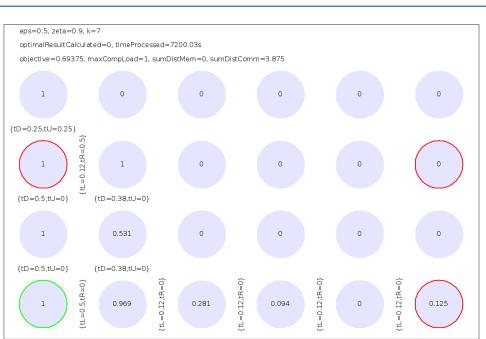

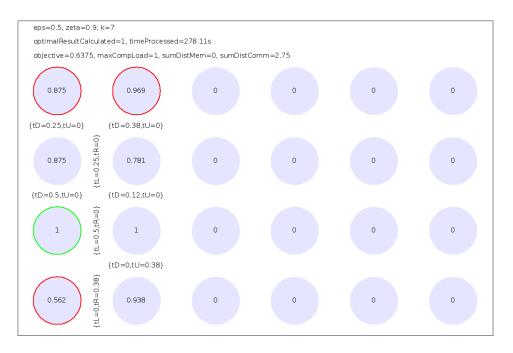

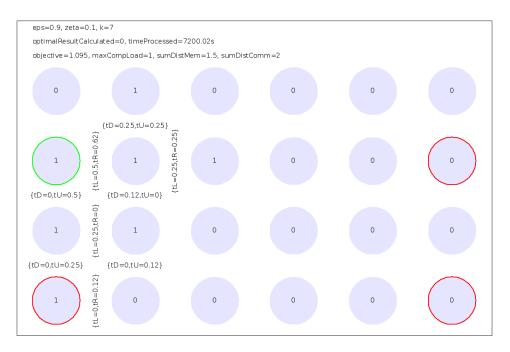

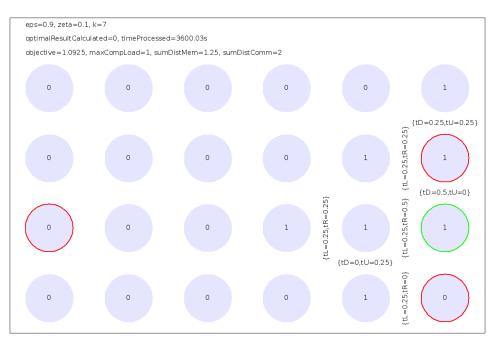

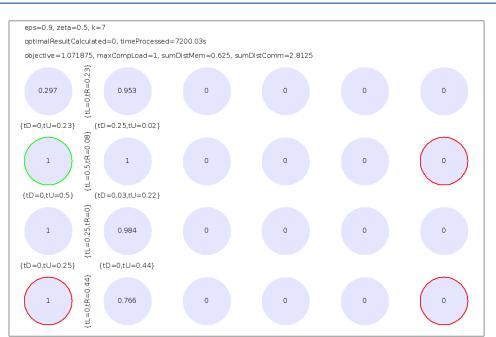

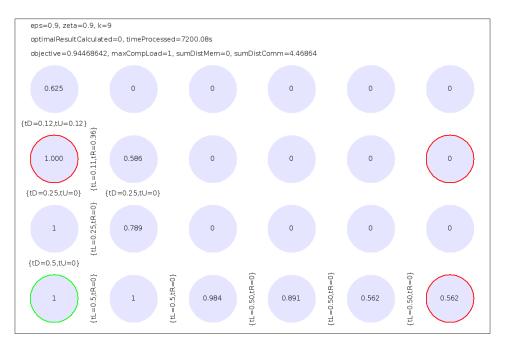

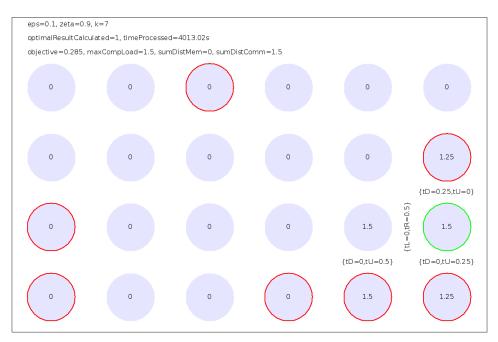

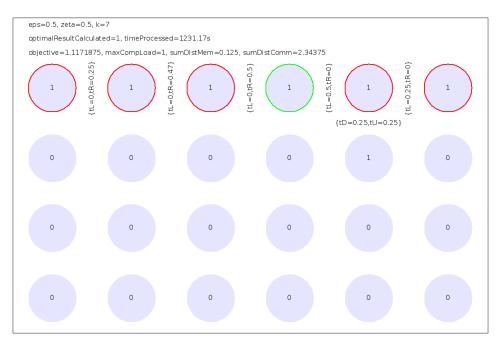

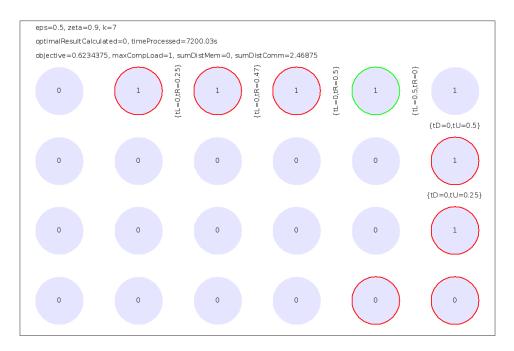

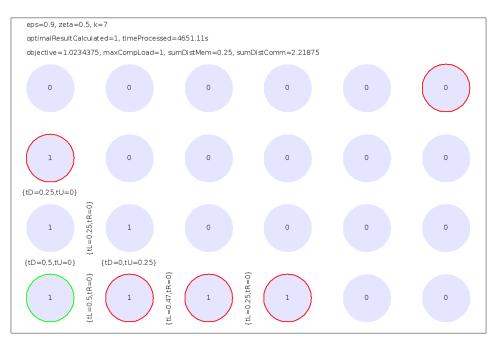

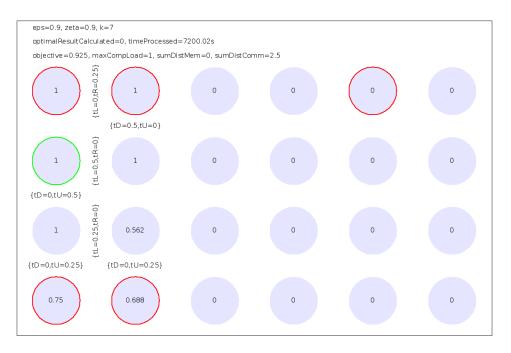

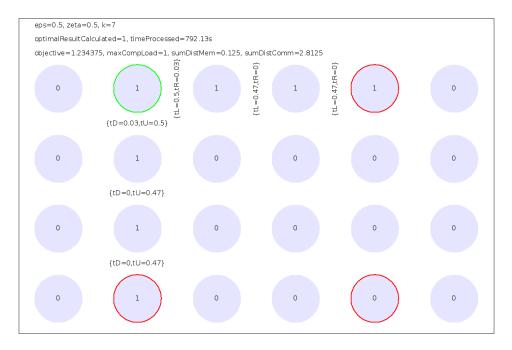

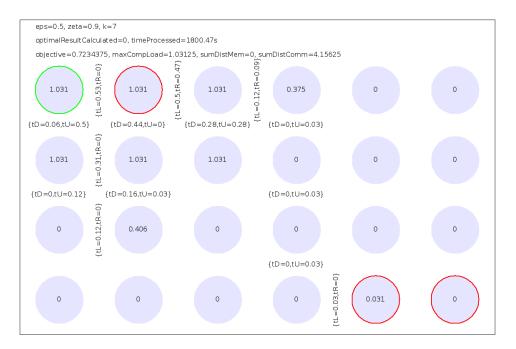

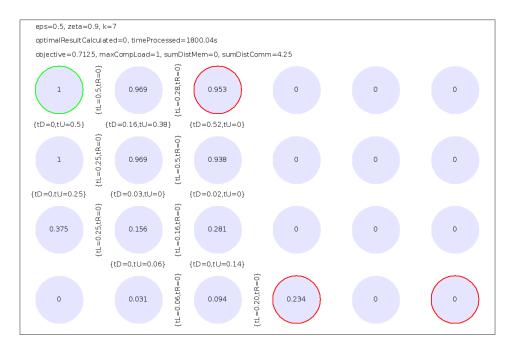

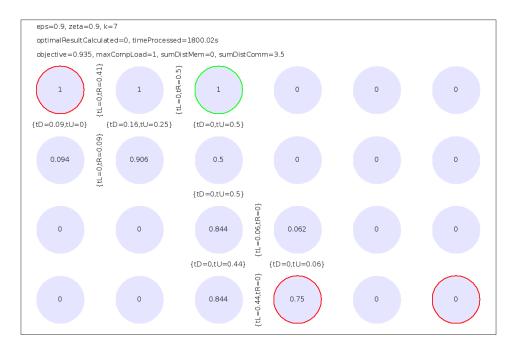

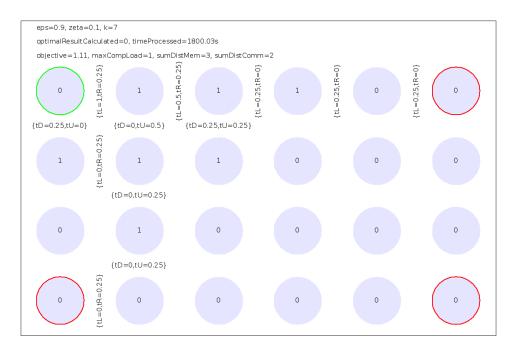

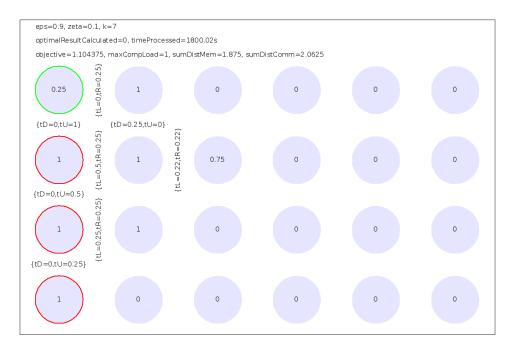

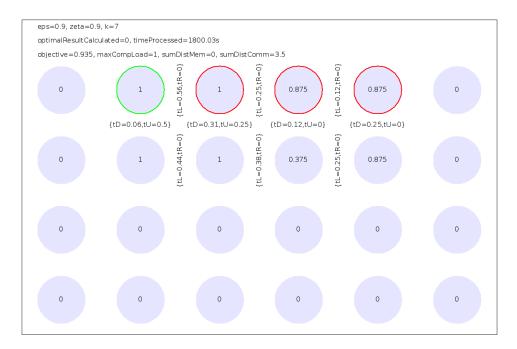

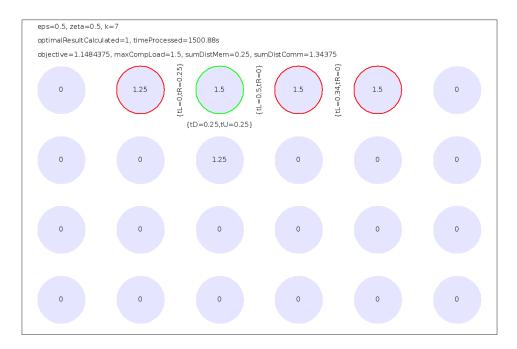

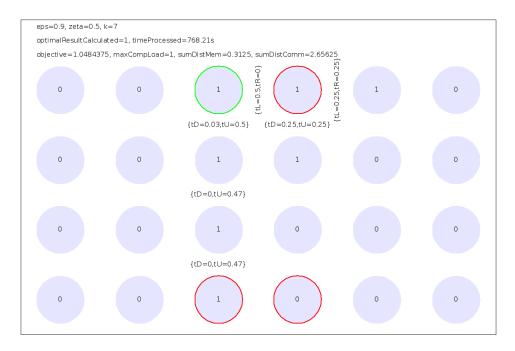

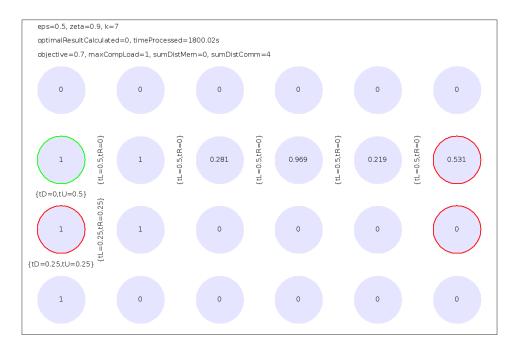

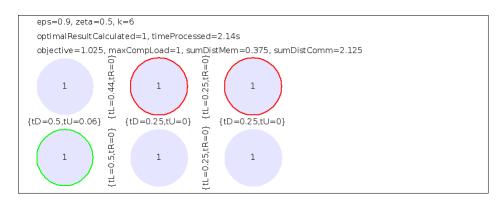

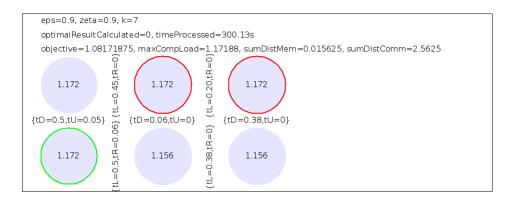

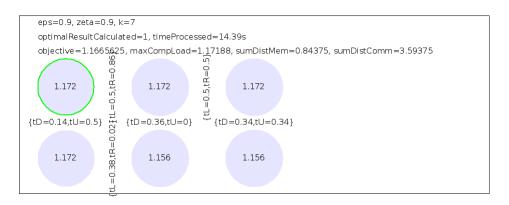

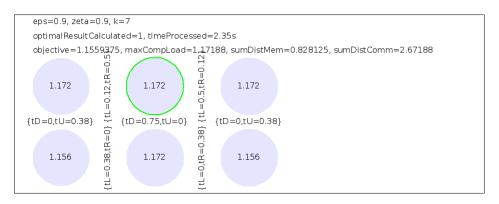

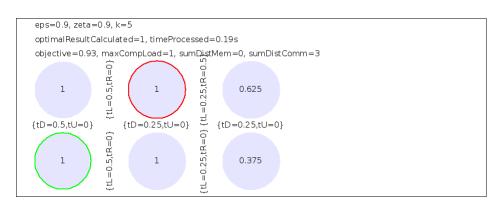

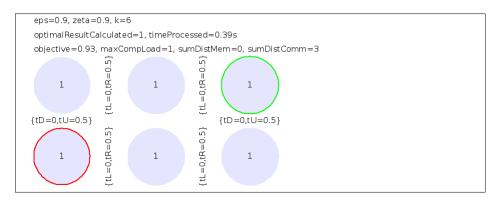

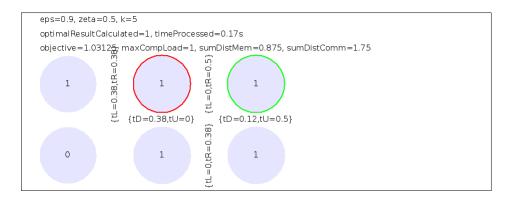

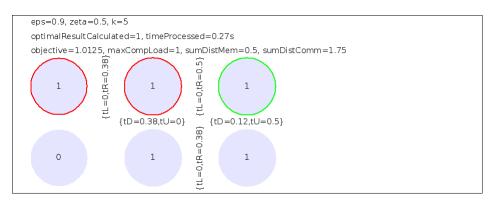

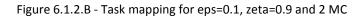

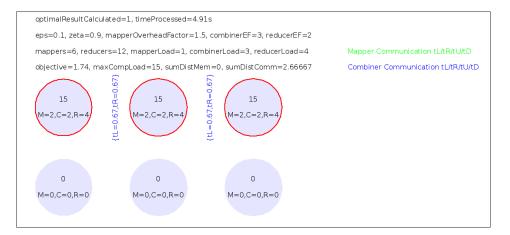

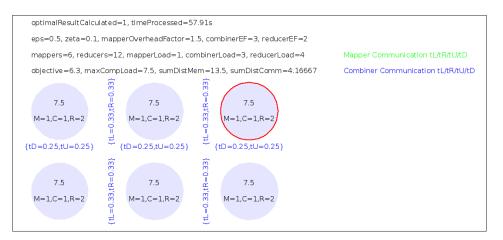

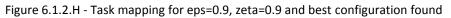

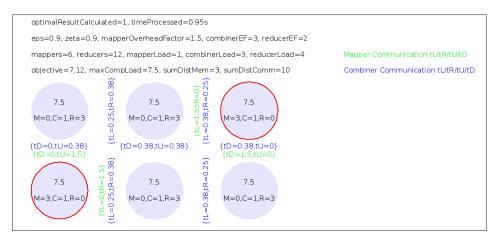

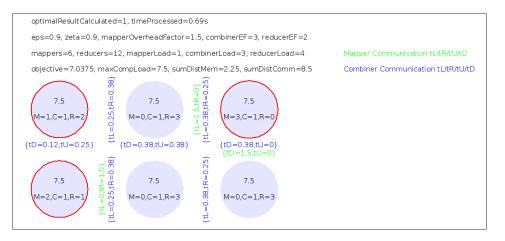

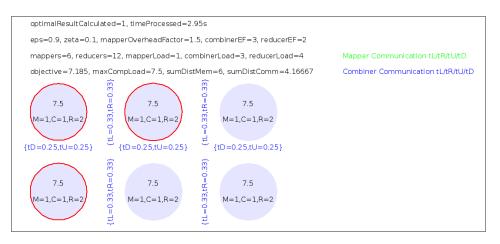

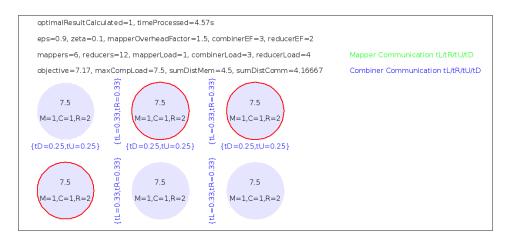

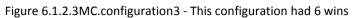

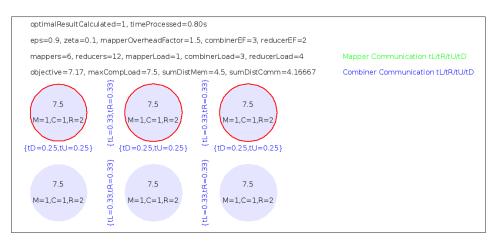

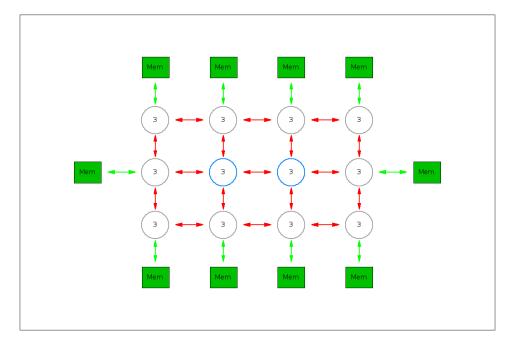

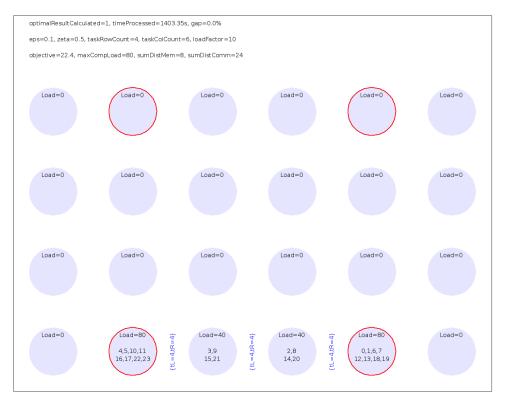

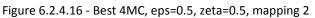

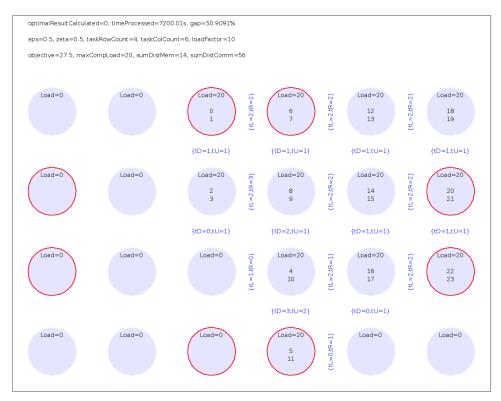

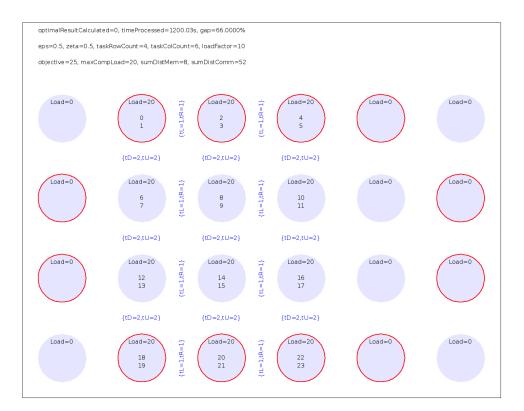

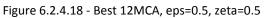

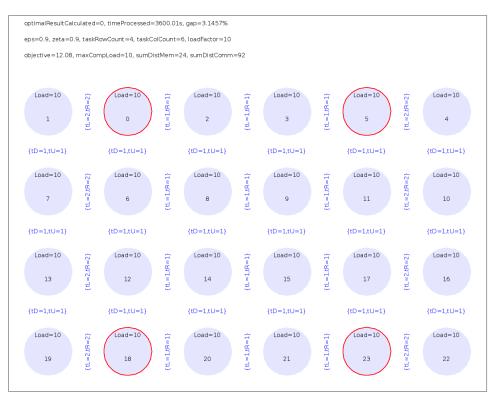

This drawing was automatically generated from the result dump of the Gurobi model execution. Its 4 rows and 6 columns represent the node structure of the Intel SCC. One node stands for 2 cores or one tile. The colored ones are the tiles with an attached memory controller. The green one is the root node meaning the one node where to root co-task is mapped to. As there is no communication between the nodes for this configuration, there is no such information available here. The legend at the top part summarizes the run details. Most are self-explaining. The parameter "optimalResultCalculated" tells whether the Gurobi run did fully finish the linear optimization or was stopped after a time limit (in most of such runs 2 hours).

As the computation costs are not important here, the relation between the communication and the memory controller distance becomes the key factor. If the communication costs relation is as high as here, it doesn't matter where the memory controllers are placed. All tasks are mapped to a single node to enforce the low node communication costs subject.

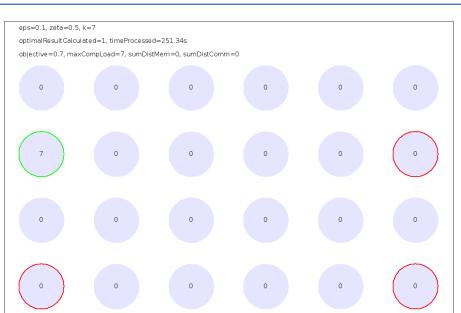

## A2) communication costs predominate computation costs AND node distance costs are weighted equally to memory controller distance costs

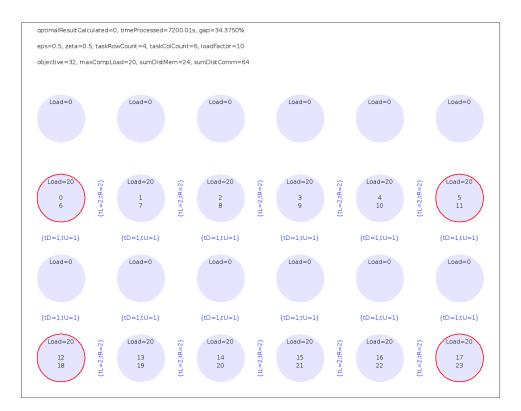

Figure 5.1.A21 - Intel SCC task and memory controller mapping

One can see that there is no difference to the setup with zeta=0.1.

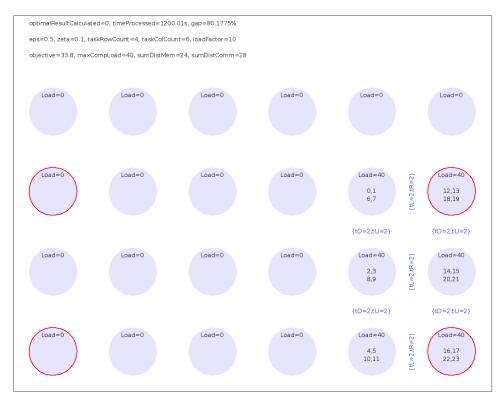

Figure 5.1.A22 – Best task and memory controller mapping

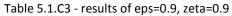

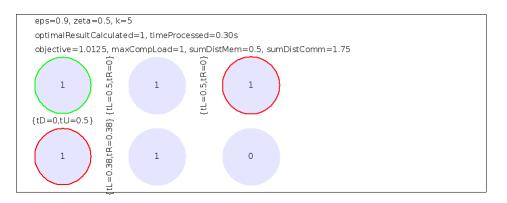

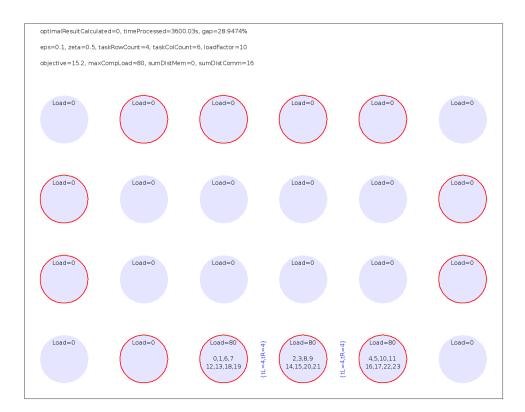

This picture demonstrates the communication part as well. "tU" means to upper nodes, "tD" means downward, "tL" to left nodes and "tR" means to send data to the right tile. The

communication path illustrated in the figures also includes the memory controller communication part which is 0 here but becomes important later.

Compared to zeta=0.1 this result makes more use of parallelization as 3 memory controllers are next to each other and the communication costs part has less influence over the other subject parts. Of course, two memory controllers next to each other would be sufficient as the third one is not mapped to by any task. As the importance of a low memory controller distance is now even bigger, the mapping of leaf tasks and the root task remains the same. They are still bounded to the memory controller tiles.

The result of optimizing the cluster is a lower subject and therefore faster sort algorithm for this configuration.